Xilinx Setup to edit config for 7i92T

- StoneB

- Offline

- New Member

-

Less

More

- Posts: 17

- Thank you received: 2

26 Nov 2024 22:09 - 26 Nov 2024 22:10 #315321

by StoneB

Xilinx Setup to edit config for 7i92T was created by StoneB

Hello, I am trying to set up my 7i92T for my existing controller (a Mechapro Slider SFX), and am struggling with the very first step: I have tried the two computers in the house (Windows 11) and both refuse to install the Xilinx Software ("Virtualization needs to be enabled"). I have made sure the BIOS virtualization is on, and have also tried some youtube trick to install Oracle Virtualbox already - but no success so far.

Is there any further trick I miss?

Alternatively, I thought I could use Raspi I want to run LinuxCNC on, but I have no idea if I can install the 4 .xz packages: do I need to unzip them all four in the same folder? How do I trigger install on Linux?

Or, if anybody has the software already installed for a 7i92T, would you be willing to program it with the below ports?

Thank you!!

Is there any further trick I miss?

Alternatively, I thought I could use Raspi I want to run LinuxCNC on, but I have no idea if I can install the 4 .xz packages: do I need to unzip them all four in the same folder? How do I trigger install on Linux?

Or, if anybody has the software already installed for a 7i92T, would you be willing to program it with the below ports?

Thank you!!

P2: LPT 1 (Slider SFX)

IO Connections for P2

DB25 pin# I/O Pri. funk Sec. func Chan Sec. Pin func Sec. Pin Dir

1 0 IOPort None

14 1 IOPort PWM 1 PWM (Out)

2 2 IOPort StepGen 0 Dir/Table2 (Out)

15 3 IOPort None

3 4 IOPort StepGen 0 Step/Table1 (Out)

16 5 IOPort PWM 1 PWM (Out) (Toggle @ 250Mhz: Assume it needs to be a PWM)

4 6 IOPort StepGen 1 Dir/Table1 (Out)

17 7 IOPort None

5 8 IOPort StepGen 1 Step/Table1 (Out)

6 9 IOPort StepGen 2 Dir/Table2 (Out)

7 10 IOPort StepGen 2 Step/Table1 (Out)

8 11 IOPort StepGen 3 Dir/Table2 (Out)

9 12 IOPort StepGen 3 Step/Table1 (Out)

10 13 IOPort None

11 14 IOPort None

12 15 IOPort None

13 16 IOPort None

P1: IO & Encoder (Pendant & Future Spindle)

IO Connections for P1

DB25 pin# I/O Pri. func Sec. func Chan Sec. Pin func Sec. Pin Dir

1 17 IOPort None

14 18 IOPort QCount 1 Quad-A (In)

2 19 IOPort None

15 20 IOPort QCount 1 Quad-B (In)

3 21 IOPort None

16 22 IOPort QCount 1 Quad-IDX (In)

4 23 IOPort None

17 24 IOPort None

5 25 IOPort None

6 26 IOPort None

7 27 IOPort None

8 28 IOPort None

9 29 IOPort None

10 30 IOPort QCount 1 Quad-A (In)

11 31 IOPort QCount 1 Quad-B (In)

12 32 IOPort QCount 1 Quad-IDX (In)

13 33 IOPort None

Slider SFX Pinout

Pin 1 Relay 1, e.g. main spindle on/off

Pin 2 Direction motor X

Pin 3 Clock motor X

Pin 4 Direction motor Y

Pin 5 Clock motor Y

Pin 6 Direction motor Z

Pin 7 Clock motor Z

Pin 8 Direction motor 4

Pin 9 Clock motor 4

Pin 10-13 Forwarded inputs, e.g. for signals from limit and

reference switches

Pin 14 PWM signal

Pin 15 Output for ready signal

Pin 16 Toggle signal

Pin 17 Current reduction input (active low)

Pin 18-25 Signal ground (0V, GND)

Last edit: 26 Nov 2024 22:10 by StoneB.

Please Log in or Create an account to join the conversation.

- Cant do this anymore bye all

-

- Offline

- Platinum Member

-

Less

More

- Posts: 1200

- Thank you received: 425

26 Nov 2024 22:50 #315326

by Cant do this anymore bye all

Replied by Cant do this anymore bye all on topic Xilinx Setup to edit config for 7i92T

Regrading the Rpi there is a pre made image. Look on the Linuxcnc home page and go to the downloads section.

Regarding Xilinx ISE I can't recall having to have Virtualization on. Make sure you are using ISE 14.7 or less as Vivado doesn't support the spartan 6.

Pete from Mesa will usually build a new config for users, so just be patient.

For info on installing ISE

wiki.linuxcnc.org/cgi-bin/wiki.pl?Editing_MESA_Bitfiles

Unfornately the images are unavailable.

Regarding Xilinx ISE I can't recall having to have Virtualization on. Make sure you are using ISE 14.7 or less as Vivado doesn't support the spartan 6.

Pete from Mesa will usually build a new config for users, so just be patient.

For info on installing ISE

wiki.linuxcnc.org/cgi-bin/wiki.pl?Editing_MESA_Bitfiles

Unfornately the images are unavailable.

Please Log in or Create an account to join the conversation.

- PCW

-

- Away

- Moderator

-

Less

More

- Posts: 17820

- Thank you received: 5213

26 Nov 2024 23:13 - 26 Nov 2024 23:14 #315329

by PCW

Replied by PCW on topic Xilinx Setup to edit config for 7i92T

If you have a 7I92T you need the Efinix tool set (Efinity) not the Xilinx tool set

The pinout looks almost identical to the G540 pinout except the step/dir pins are swapped,

so 7i92t_g540d.bin could be used if it's not too much of an issue to physically swap the

step/dir pins.

Note that for the charge-pump, a stepgen is normally used (and pncconf knows how to set this up)

If swapping the step/dir pins is too much of a pain, I can either build firmware with the more advanced stepgens

the can swap output pins (so its still a g540 configuration but with some added stepgen features)

or make a custom configuration. It is a fair nuisance to setup the tools so maybe not worth it for one configuration

that I can do a a few minutes.

The pinout looks almost identical to the G540 pinout except the step/dir pins are swapped,

so 7i92t_g540d.bin could be used if it's not too much of an issue to physically swap the

step/dir pins.

Note that for the charge-pump, a stepgen is normally used (and pncconf knows how to set this up)

If swapping the step/dir pins is too much of a pain, I can either build firmware with the more advanced stepgens

the can swap output pins (so its still a g540 configuration but with some added stepgen features)

or make a custom configuration. It is a fair nuisance to setup the tools so maybe not worth it for one configuration

that I can do a a few minutes.

Last edit: 26 Nov 2024 23:14 by PCW.

Please Log in or Create an account to join the conversation.

- Cant do this anymore bye all

-

- Offline

- Platinum Member

-

Less

More

- Posts: 1200

- Thank you received: 425

27 Nov 2024 03:06 #315337

by Cant do this anymore bye all

Replied by Cant do this anymore bye all on topic Xilinx Setup to edit config for 7i92T

My only excuse is it 3 million degrees Celsius in Sydney ATM

Please Log in or Create an account to join the conversation.

- StoneB

- Offline

- New Member

-

Less

More

- Posts: 17

- Thank you received: 2

08 Dec 2024 10:34 #316238

by StoneB

Replied by StoneB on topic Xilinx Setup to edit config for 7i92T

Thanks PCW and cornholio for your pointers!

I would really want to try a custom firmware as the card will interface with two pre-existing connectors / controllers within a very tight space - adding a DB25 cable which reroutes the ports will be an absolute pain

I have now Efinix loaded and running, and I have found how to load the 7i92t-hm2 project (I assume from other forum posts that the 7i92t25 is for larger projects and so not applicable for me). I'm not able to find a pointer as to where to edit my pins? I read that I need to edit seveni92t.peri.xml but that file looks daunting: how I find which pins (of the two ports) are meant?

Also, thanks for the pointer regarding toggle: I have amended my notes, does it work to have just one Step, or do they need to come in step/dir pairs?

Thanks for your patient help

I would really want to try a custom firmware as the card will interface with two pre-existing connectors / controllers within a very tight space - adding a DB25 cable which reroutes the ports will be an absolute pain

I have now Efinix loaded and running, and I have found how to load the 7i92t-hm2 project (I assume from other forum posts that the 7i92t25 is for larger projects and so not applicable for me). I'm not able to find a pointer as to where to edit my pins? I read that I need to edit seveni92t.peri.xml but that file looks daunting: how I find which pins (of the two ports) are meant?

Also, thanks for the pointer regarding toggle: I have amended my notes, does it work to have just one Step, or do they need to come in step/dir pairs?

P2: LPT 1 (Slider SFX)

IO Connections for P2

DB25 pin# I/O Pri. funk Sec. func Chan Sec. Pin func Sec. Pin Dir

1 0 IOPort None

14 1 IOPort PWM 1 PWM (Out)

2 2 IOPort StepGen 0 Dir/Table2 (Out)

15 3 IOPort None

3 4 IOPort StepGen 0 Step/Table1 (Out)

16 5 IOPort StepGen 4 Step/Table1 (Out) (Toggle 250Mhz PWM)

4 6 IOPort StepGen 1 Dir/Table1 (Out)

17 7 IOPort None

5 8 IOPort StepGen 1 Step/Table1 (Out)

6 9 IOPort StepGen 2 Dir/Table2 (Out)

7 10 IOPort StepGen 2 Step/Table1 (Out)

8 11 IOPort StepGen 3 Dir/Table2 (Out)

9 12 IOPort StepGen 3 Step/Table1 (Out)

10 13 IOPort None

11 14 IOPort None

12 15 IOPort None

13 16 IOPort None

P1: IO & Encoder (Pendant & Future Spindle)

IO Connections for P1

DB25 pin# I/O Pri. func Sec. func Chan Sec. Pin func Sec. Pin Dir

1 17 IOPort None

14 18 IOPort QCount 1 Quad-A (In)

2 19 IOPort None

15 20 IOPort QCount 1 Quad-B (In)

3 21 IOPort None

16 22 IOPort QCount 1 Quad-IDX (In)

4 23 IOPort None

17 24 IOPort None

5 25 IOPort None

6 26 IOPort None

7 27 IOPort None

8 28 IOPort None

9 29 IOPort None

10 30 IOPort QCount 1 Quad-A (In)

11 31 IOPort QCount 1 Quad-B (In)

12 32 IOPort QCount 1 Quad-IDX (In)

13 33 IOPort None

Slider SFX Pinout

Pin 1 Relay 1, e.g. main spindle on/off

Pin 2 Direction motor X

Pin 3 Clock motor X

Pin 4 Direction motor Y

Pin 5 Clock motor Y

Pin 6 Direction motor Z

Pin 7 Clock motor Z

Pin 8 Direction motor 4

Pin 9 Clock motor 4

Pin 10-13 Forwarded inputs, e.g. for signals from limit and

reference switches

Pin 14 PWM signal

Pin 15 Output for ready signal

Pin 16 Toggle signal

Pin 17 Current reduction input (active low)

Pin 18-25 Signal ground (0V, GND)Thanks for your patient help

Please Log in or Create an account to join the conversation.

- PCW

-

- Away

- Moderator

-

Less

More

- Posts: 17820

- Thank you received: 5213

08 Dec 2024 14:15 - 08 Dec 2024 14:35 #316246

by PCW

Replied by PCW on topic Xilinx Setup to edit config for 7i92T

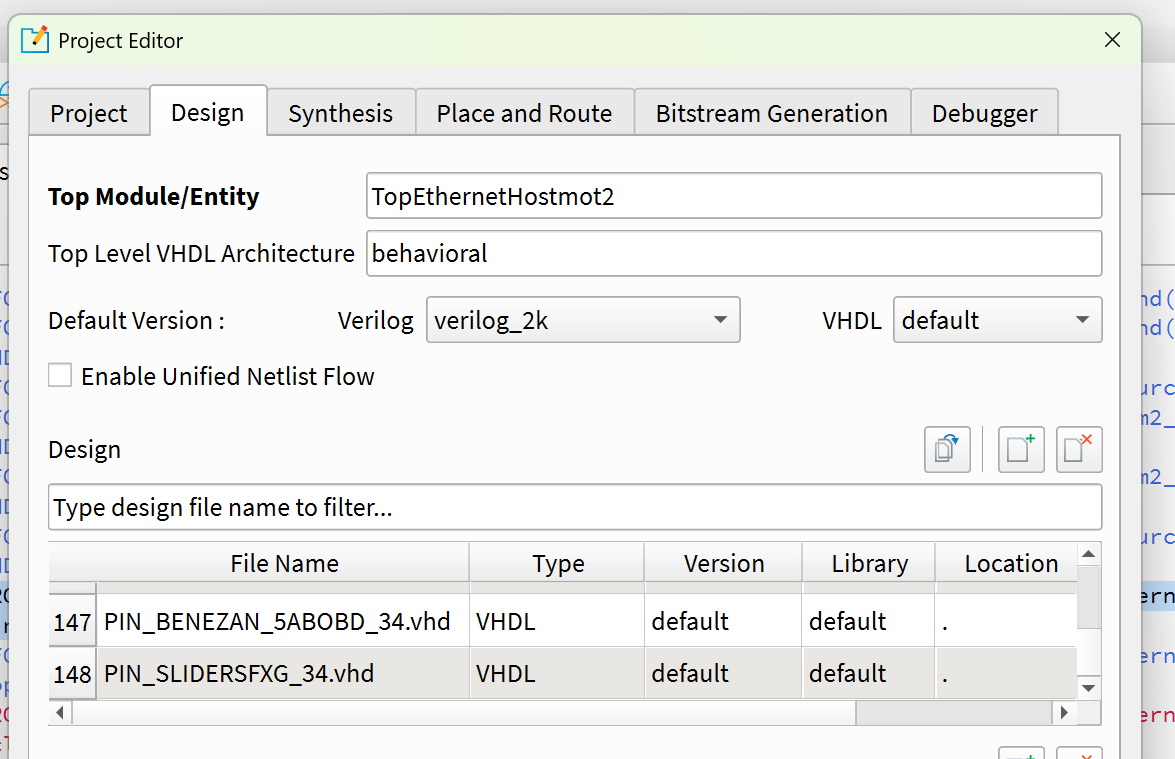

The pinout is determined by the pinout file (PINXXXX.vhd)

This file is identical for Xilinx or Efinix chips. Basically to make

a new pinout, you copy an existing pinout file ( one that's similar

to what you want) to your new pinout file, edit that file to match

the required pinout and module counts. Add that new file to

the project (with "Edit Project" --> "Design" --> "Add design file")

and include it in the toplevel source file (TopEthernet16HostMot2_efx.vhd)

by adding it like this:

--use work.PIN_7I85SD_7I76_SSI_34.all;

--use work.PIN_PMDX126x2_34.all;

use work.PIN_NEWPINOUTFILE_34.all; <<<<<<<<

--use work.PIN_7I85S_4PWMD_34.all;

--use work.PIN_APSX_SWISS.all;

--use work.PIN_IOONLY_34.all;

--use work.PIN_ST8_RC8_34.all;

Note that only one pinout file is uncommented

The .xml files are for the project manager and the interface designer

you do not edit them directly, nor do you change anything with the interface

designer unless you have different hardware (a custom FPGA card for example)

This file is identical for Xilinx or Efinix chips. Basically to make

a new pinout, you copy an existing pinout file ( one that's similar

to what you want) to your new pinout file, edit that file to match

the required pinout and module counts. Add that new file to

the project (with "Edit Project" --> "Design" --> "Add design file")

and include it in the toplevel source file (TopEthernet16HostMot2_efx.vhd)

by adding it like this:

--use work.PIN_7I85SD_7I76_SSI_34.all;

--use work.PIN_PMDX126x2_34.all;

use work.PIN_NEWPINOUTFILE_34.all; <<<<<<<<

--use work.PIN_7I85S_4PWMD_34.all;

--use work.PIN_APSX_SWISS.all;

--use work.PIN_IOONLY_34.all;

--use work.PIN_ST8_RC8_34.all;

Note that only one pinout file is uncommented

The .xml files are for the project manager and the interface designer

you do not edit them directly, nor do you change anything with the interface

designer unless you have different hardware (a custom FPGA card for example)

Last edit: 08 Dec 2024 14:35 by PCW.

Please Log in or Create an account to join the conversation.

- StoneB

- Offline

- New Member

-

Less

More

- Posts: 17

- Thank you received: 2

13 Dec 2024 12:23 - 13 Dec 2024 12:24 #316572

by StoneB

Replied by StoneB on topic Xilinx Setup to edit config for 7i92T

I think I made all the modifications needed (and included my PIN_Slidersfx file in the TopEthernet16HostMot2_efx).

When I now try to synthesize, I get the error "pin_slidersfxg_34 not compiled in library 'gui_analyze'. Should I call my file in another file too?

Thanks!

When I now try to synthesize, I get the error "pin_slidersfxg_34 not compiled in library 'gui_analyze'. Should I call my file in another file too?

Thanks!

Last edit: 13 Dec 2024 12:24 by StoneB.

Please Log in or Create an account to join the conversation.

- PCW

-

- Away

- Moderator

-

Less

More

- Posts: 17820

- Thank you received: 5213

13 Dec 2024 15:40 #316582

by PCW

Replied by PCW on topic Xilinx Setup to edit config for 7i92T

Did you add your new pin file to the project?

Please Log in or Create an account to join the conversation.

- StoneB

- Offline

- New Member

-

Less

More

- Posts: 17

- Thank you received: 2

13 Dec 2024 17:10 #316597

by StoneB

Replied by StoneB on topic Xilinx Setup to edit config for 7i92T

I did - it appears in the design - that's how it should be, right?

The error that stops Synthesis is:ERROR : ***\7i92t\configs\hostmot2\source\7i92t-hm2\TopEthernet16HostMot2_efx.vhd(135): 'pin_slidersfxg_34' is not compiled in library 'efxlib' [VHDL-1240]

Here are my two edited files:

The error that stops Synthesis is:ERROR : ***\7i92t\configs\hostmot2\source\7i92t-hm2\TopEthernet16HostMot2_efx.vhd(135): 'pin_slidersfxg_34' is not compiled in library 'efxlib' [VHDL-1240]

Here are my two edited files:

Attachments:

Please Log in or Create an account to join the conversation.

- PCW

-

- Away

- Moderator

-

Less

More

- Posts: 17820

- Thank you received: 5213

13 Dec 2024 17:53 #316600

by PCW

Replied by PCW on topic Xilinx Setup to edit config for 7i92T

You have the old (G540) package name in your pinout file

Please Log in or Create an account to join the conversation.

Moderators: PCW, jmelson

Time to create page: 0.160 seconds