7i76e with 7i85 strange encoder output

- Nitram

-

Topic Author

Topic Author

- Offline

- Elite Member

-

Less

More

- Posts: 210

- Thank you received: 15

12 Aug 2018 17:29 #115976

by Nitram

Replied by Nitram on topic 7i76e with 7i85 strange encoder output

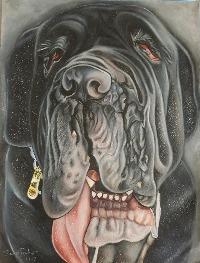

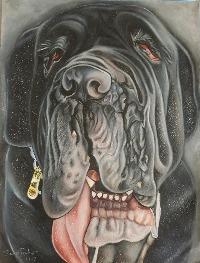

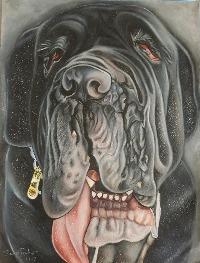

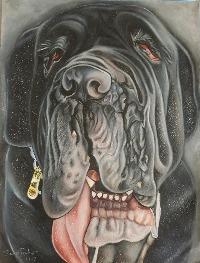

As a further check, on the 7i85 board are U7 and RN12 and RN13 supposed to be unpopulated?

I took a look at the 7i85 picture from the webpage and whilst it is not super sharp it does appear that those spots are similarly unpopulated. just thought i'd confirm though.

Thanks.

I took a look at the 7i85 picture from the webpage and whilst it is not super sharp it does appear that those spots are similarly unpopulated. just thought i'd confirm though.

Thanks.

Please Log in or Create an account to join the conversation.

- PCW

-

- Online

- Moderator

-

Less

More

- Posts: 17820

- Thank you received: 5213

12 Aug 2018 17:32 #115977

by PCW

Replied by PCW on topic 7i76e with 7i85 strange encoder output

Yes, there are two assembly options using the same 7I85 PCB: the 7I85 and the 7I85S.

Please Log in or Create an account to join the conversation.

- Nitram

-

Topic Author

Topic Author

- Offline

- Elite Member

-

Less

More

- Posts: 210

- Thank you received: 15

12 Aug 2018 17:33 #115978

by Nitram

Replied by Nitram on topic 7i76e with 7i85 strange encoder output

Have tested the cable following your first post, but will make up another cable tomorrow (it is currently 3.30am here) to be absolutely sure to exclude that side of things.

I'll report back following that but after having checked the cable including a specific test of IO27 from the rear of the boards via the cable, my gut tells me a 7i85 issue??

I'll report back following that but after having checked the cable including a specific test of IO27 from the rear of the boards via the cable, my gut tells me a 7i85 issue??

Please Log in or Create an account to join the conversation.

- Nitram

-

Topic Author

Topic Author

- Offline

- Elite Member

-

Less

More

- Posts: 210

- Thank you received: 15

13 Aug 2018 03:06 #115986

by Nitram

Replied by Nitram on topic 7i76e with 7i85 strange encoder output

Hi Peter.

Tested with a different cable this morning. No change unfortunately.

Results are the same as before i.e. enc slot 0 = nothing, enc slot 1 = counts on 0&1, enc slot 2 = nothing, enc slot 3 = counts on 2&3.

With the cabling excluded from being the culprit of no EncMuxSel output, I suspect it is now reasonable to suspect the 8i85 board as you've suggested?

Thanks,

Marty.

Tested with a different cable this morning. No change unfortunately.

Results are the same as before i.e. enc slot 0 = nothing, enc slot 1 = counts on 0&1, enc slot 2 = nothing, enc slot 3 = counts on 2&3.

With the cabling excluded from being the culprit of no EncMuxSel output, I suspect it is now reasonable to suspect the 8i85 board as you've suggested?

Thanks,

Marty.

Please Log in or Create an account to join the conversation.

- PCW

-

- Online

- Moderator

-

Less

More

- Posts: 17820

- Thank you received: 5213

13 Aug 2018 18:47 #116013

by PCW

Replied by PCW on topic 7i76e with 7i85 strange encoder output

Yeah unless its a funny hal file setting (too high sample rate or some such), it looks like a failed 7I85

The following user(s) said Thank You: Nitram

Please Log in or Create an account to join the conversation.

- Nitram

-

Topic Author

Topic Author

- Offline

- Elite Member

-

Less

More

- Posts: 210

- Thank you received: 15

14 Aug 2018 00:08 #116019

by Nitram

Replied by Nitram on topic 7i76e with 7i85 strange encoder output

Thanks for your help with this Peter.

Your previous post on sample rates gnawed at me during my sleep and at 5am I went back and checked hal and ini data.

I was able to resolve the issue and was able to replicate what was happening.

When I went back to the ini file, I noticed that that servo period was 10000000 rather than the usual default of 1000000 (i.e. one extra zero).

This resulted in the servo period exceeding the watchdog timout in the hal file (being 5000000).

Thus on the computer I was using to test the boards, the watchdog bit, stopping any outputs from the cards.

The irony in this was that via HAL watch, I could see the encoder counts changing and thought the pairing lay with a fault within either the card or the cable, rather than realizing the much more subtle fact that in this scenario, inputs were getting through (encoder counts) but outputs (mux pin) was being blocked by the watchdog.

As soon as either the servo period was reduced below the watchdog threshold or the watchdog threshold was increased above the servo period the watchdog stopped biting and allowed outputs again, thus allowing the mux pin output to divide the encoders correctly, assigning them to their correct individual outputs.

In this case, it didn't throw up any error messages in Axis when the watchdog bit, and the subtle nature of issue (allowing inputs but blocking outputs) threw a curve ball.

Wanted to again say a big thank you to Peter for his time and help in steering the way on getting to the bottom of this and I hope this post might help others in the future.

Regards,

Marty.

Your previous post on sample rates gnawed at me during my sleep and at 5am I went back and checked hal and ini data.

I was able to resolve the issue and was able to replicate what was happening.

When I went back to the ini file, I noticed that that servo period was 10000000 rather than the usual default of 1000000 (i.e. one extra zero).

This resulted in the servo period exceeding the watchdog timout in the hal file (being 5000000).

Thus on the computer I was using to test the boards, the watchdog bit, stopping any outputs from the cards.

The irony in this was that via HAL watch, I could see the encoder counts changing and thought the pairing lay with a fault within either the card or the cable, rather than realizing the much more subtle fact that in this scenario, inputs were getting through (encoder counts) but outputs (mux pin) was being blocked by the watchdog.

As soon as either the servo period was reduced below the watchdog threshold or the watchdog threshold was increased above the servo period the watchdog stopped biting and allowed outputs again, thus allowing the mux pin output to divide the encoders correctly, assigning them to their correct individual outputs.

In this case, it didn't throw up any error messages in Axis when the watchdog bit, and the subtle nature of issue (allowing inputs but blocking outputs) threw a curve ball.

Wanted to again say a big thank you to Peter for his time and help in steering the way on getting to the bottom of this and I hope this post might help others in the future.

Regards,

Marty.

Please Log in or Create an account to join the conversation.

- andypugh

-

- Offline

- Moderator

-

Less

More

- Posts: 19831

- Thank you received: 4623

16 Aug 2018 12:38 #116133

by andypugh

Replied by andypugh on topic 7i76e with 7i85 strange encoder output

Well spotted.

Please Log in or Create an account to join the conversation.

Moderators: PCW, jmelson

Time to create page: 0.079 seconds