hostmot2 decode process question

- Spacehitchhiker42

-

Topic Author

Topic Author

- Offline

- New Member

-

Less

More

- Posts: 17

- Thank you received: 1

13 Feb 2019 22:41 #126406

by Spacehitchhiker42

hostmot2 decode process question was created by Spacehitchhiker42

Hi all, I'm working on a hostmot2 firmware for a cyclone FPGA,and i was wondering why the different modules are decoded in the main hostmot2 file instead of in their own files.

for instance why use

why not just handle the address decoding inside the stepgen?

for instance why use

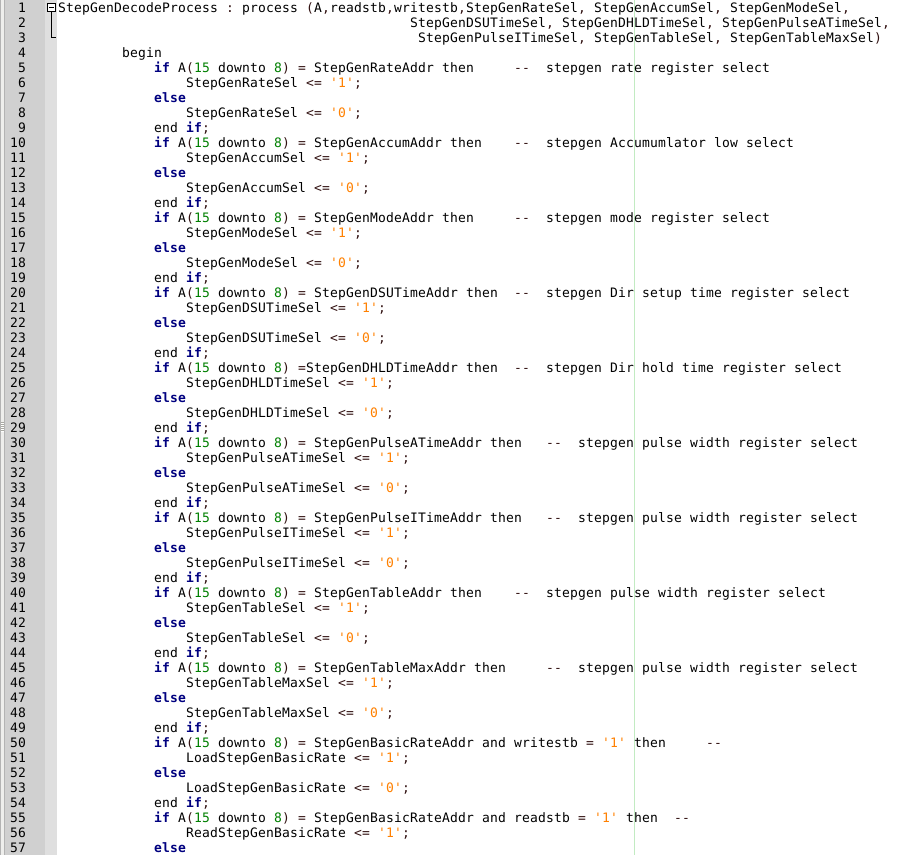

StepGenDecodeProcess : process (A,readstb,writestb,StepGenRateSel, StepGenAccumSel, StepGenModeSel,

StepGenDSUTimeSel, StepGenDHLDTimeSel, StepGenPulseATimeSel,

StepGenPulseITimeSel, StepGenTableSel, StepGenTableMaxSel)

begin

if A(15 downto 8) = StepGenRateAddr then -- stepgen rate register select

StepGenRateSel <= '1';

else

StepGenRateSel <= '0';

end if;

if A(15 downto 8) = StepGenAccumAddr then -- stepgen Accumumlator low select

StepGenAccumSel <= '1';

else

StepGenAccumSel <= '0';

end if;

if A(15 downto 8) = StepGenModeAddr then -- stepgen mode register select

StepGenModeSel <= '1';

else

StepGenModeSel <= '0';

end if;

if A(15 downto 8) = StepGenDSUTimeAddr then -- stepgen Dir setup time register select

StepGenDSUTimeSel <= '1';

else

StepGenDSUTimeSel <= '0';

end if;

if A(15 downto 8) =StepGenDHLDTimeAddr then -- stepgen Dir hold time register select

StepGenDHLDTimeSel <= '1';

else

StepGenDHLDTimeSel <= '0';

end if;

if A(15 downto 8) = StepGenPulseATimeAddr then -- stepgen pulse width register select

StepGenPulseATimeSel <= '1';

else

StepGenPulseATimeSel <= '0';

end if;

if A(15 downto 8) = StepGenPulseITimeAddr then -- stepgen pulse width register select

StepGenPulseITimeSel <= '1';

else

StepGenPulseITimeSel <= '0';

end if;

if A(15 downto 8) = StepGenTableAddr then -- stepgen pulse width register select

StepGenTableSel <= '1';

else

StepGenTableSel <= '0';

end if;

if A(15 downto 8) = StepGenTableMaxAddr then -- stepgen pulse width register select

StepGenTableMaxSel <= '1';

else

StepGenTableMaxSel <= '0';

end if;

if A(15 downto 8) = StepGenBasicRateAddr and writestb = '1' then --

LoadStepGenBasicRate <= '1';

else

LoadStepGenBasicRate <= '0';

end if;

if A(15 downto 8) = StepGenBasicRateAddr and readstb = '1' then --

ReadStepGenBasicRate <= '1';

else

ReadStepGenBasicRate <= '0';

end if;

LoadStepGenRate <= OneOfNDecode(STEPGENs,StepGenRateSel,writestb,A(7 downto 2)); -- 64 max

ReadStepGenRate <= OneOfNDecode(STEPGENs,StepGenRateSel,readstb,A(7 downto 2)); -- Note: all the reads are decoded here

LoadStepGenAccum <= OneOfNDecode(STEPGENs,StepGenAccumSel,writestb,A(7 downto 2)); -- but most are commented out in the

ReadStepGenAccum <= OneOfNDecode(STEPGENs,StepGenAccumSel,readstb,A(7 downto 2)); -- stepgen module hardware for space reasons

LoadStepGenMode <= OneOfNDecode(STEPGENs,StepGenModeSel,writestb,A(7 downto 2));

ReadStepGenMode <= OneOfNDecode(STEPGENs,StepGenModeSel,Readstb,A(7 downto 2));

LoadStepGenDSUTime <= OneOfNDecode(STEPGENs,StepGenDSUTimeSel,writestb,A(7 downto 2));

ReadStepGenDSUTime <= OneOfNDecode(STEPGENs,StepGenDSUTimeSel,Readstb,A(7 downto 2));

LoadStepGenDHLDTime <= OneOfNDecode(STEPGENs,StepGenDHLDTimeSel,writestb,A(7 downto 2));

ReadStepGenDHLDTime <= OneOfNDecode(STEPGENs,StepGenDHLDTimeSel,Readstb,A(7 downto 2));

LoadStepGenPulseATime <= OneOfNDecode(STEPGENs,StepGenPulseATimeSel,writestb,A(7 downto 2));

ReadStepGenPulseATime <= OneOfNDecode(STEPGENs,StepGenPulseATimeSel,Readstb,A(7 downto 2));

LoadStepGenPulseITime <= OneOfNDecode(STEPGENs,StepGenPulseITimeSel,writestb,A(7 downto 2));

ReadStepGenPulseITime <= OneOfNDecode(STEPGENs,StepGenPulseITimeSel,Readstb,A(7 downto 2));

LoadStepGenTable <= OneOfNDecode(STEPGENs,StepGenTableSel,writestb,A(7 downto 2));

ReadStepGenTable <= OneOfNDecode(STEPGENs,StepGenTableSel,Readstb,A(7 downto 2));

LoadStepGenTableMax <= OneOfNDecode(STEPGENs,StepGenTableMaxSel,writestb,A(7 downto 2));

ReadStepGenTableMax <= OneOfNDecode(STEPGENs,StepGenTableMaxSel,Readstb,A(7 downto 2));

end process StepGenDecodeProcess;why not just handle the address decoding inside the stepgen?

Please Log in or Create an account to join the conversation.

- Grotius

-

- Offline

- Platinum Member

-

Less

More

- Posts: 2419

- Thank you received: 2348

13 Feb 2019 22:56 - 13 Feb 2019 23:00 #126412

by Grotius

Replied by Grotius on topic hostmot2 decode process question

Attachments:

Last edit: 13 Feb 2019 23:00 by Grotius.

Please Log in or Create an account to join the conversation.

- PCW

-

- Offline

- Moderator

-

Less

More

- Posts: 17838

- Thank you received: 5220

13 Feb 2019 22:58 - 13 Feb 2019 22:59 #126413

by PCW

Replied by PCW on topic hostmot2 decode process question

Chiefly because I use the modules in other designs so I dont want to hardwire the hm2 decoding into the modules but rather make the specific decoding scheme bound to the upper hm2 specific layer

Last edit: 13 Feb 2019 22:59 by PCW.

Please Log in or Create an account to join the conversation.

- Spacehitchhiker42

-

Topic Author

Topic Author

- Offline

- New Member

-

Less

More

- Posts: 17

- Thank you received: 1

13 Feb 2019 23:07 #126415

by Spacehitchhiker42

Replied by Spacehitchhiker42 on topic hostmot2 decode process question

OK, that makes sense.

Please Log in or Create an account to join the conversation.

Moderators: PCW, jmelson

Time to create page: 0.149 seconds