SSI absolute encoders and analog servos

- PCW

-

- Offline

- Moderator

-

Less

More

- Posts: 17877

- Thank you received: 5236

26 Oct 2016 13:45 #82083

by PCW

Replied by PCW on topic SSI absolute encoders and analog servos

Did you set the frequency in the hal file?

Do the errors only come once?

Do the errors only come once?

Please Log in or Create an account to join the conversation.

- terkaa

- Offline

- Elite Member

-

Less

More

- Posts: 261

- Thank you received: 3

26 Oct 2016 15:09 #82086

by terkaa

Replied by terkaa on topic SSI absolute encoders and analog servos

Did you not see halscope pics I posted? Photobucket has been slow today. Yes I did with setp hm2_5i25.0.dpll.base-frequency-khz 1.007 I was able to get phase.error quite close to zero. Yes this warning comes only once. See pics above pls.

Tero

Tero

Please Log in or Create an account to join the conversation.

- PCW

-

- Offline

- Moderator

-

Less

More

- Posts: 17877

- Thank you received: 5236

26 Oct 2016 15:41 #82087

by PCW

Replied by PCW on topic SSI absolute encoders and analog servos

Yes i saw the pictures and assumed you use setp to set the base rate

my question was whether this was done in the hal file at startup or via

a halcmd later

my question was whether this was done in the hal file at startup or via

a halcmd later

Please Log in or Create an account to join the conversation.

- terkaa

- Offline

- Elite Member

-

Less

More

- Posts: 261

- Thank you received: 3

26 Oct 2016 16:28 #82091

by terkaa

Replied by terkaa on topic SSI absolute encoders and analog servos

In HAL file almost at the top. Before setting timers for SSI.

Tero

Tero

Please Log in or Create an account to join the conversation.

- PCW

-

- Offline

- Moderator

-

Less

More

- Posts: 17877

- Thank you received: 5236

26 Oct 2016 16:53 #82100

by PCW

Replied by PCW on topic SSI absolute encoders and analog servos

Do you get an error if you don't set the SSI timer channels?

If not, its probably possible to set the timer channels after the DPLL has stabilized

If not, its probably possible to set the timer channels after the DPLL has stabilized

Please Log in or Create an account to join the conversation.

- terkaa

- Offline

- Elite Member

-

Less

More

- Posts: 261

- Thank you received: 3

26 Oct 2016 18:08 #82109

by terkaa

Replied by terkaa on topic SSI absolute encoders and analog servos

I will check this tomorrow. If I do not get any, how do I set timers on after DPLL has stabilized?

Tero

Tero

Please Log in or Create an account to join the conversation.

- PCW

-

- Offline

- Moderator

-

Less

More

- Posts: 17877

- Thank you received: 5236

26 Oct 2016 19:22 #82112

by PCW

Replied by PCW on topic SSI absolute encoders and analog servos

For a test you can do it with a halcmd

it may be that it could be done in the postgui hal file

In the mean time I will look for a solution for DPLL configs where

the base clock is off by a significant amount

( This is not an issue with PCIE or Ethernet, only some PCI cards + some Motherboards )

it may be that it could be done in the postgui hal file

In the mean time I will look for a solution for DPLL configs where

the base clock is off by a significant amount

( This is not an issue with PCIE or Ethernet, only some PCI cards + some Motherboards )

Please Log in or Create an account to join the conversation.

- terkaa

- Offline

- Elite Member

-

Less

More

- Posts: 261

- Thank you received: 3

27 Oct 2016 09:29 #82136

by terkaa

Replied by terkaa on topic SSI absolute encoders and analog servos

Ok I did comment out lines setp hm2_5i25.0.ssi.0n.timer-number 4 from HAL. Then I started control. Waited for at least 5 mins. But right after using halcmd setp hm2_5i25.0.ssi.01.timer-number 4. I get same warning....

Tero

Tero

Please Log in or Create an account to join the conversation.

- PCW

-

- Offline

- Moderator

-

Less

More

- Posts: 17877

- Thank you received: 5236

27 Oct 2016 13:49 #82142

by PCW

Replied by PCW on topic SSI absolute encoders and analog servos

There may be more going on here than just the wrong base frequency

What kind of latency do you get on that system?

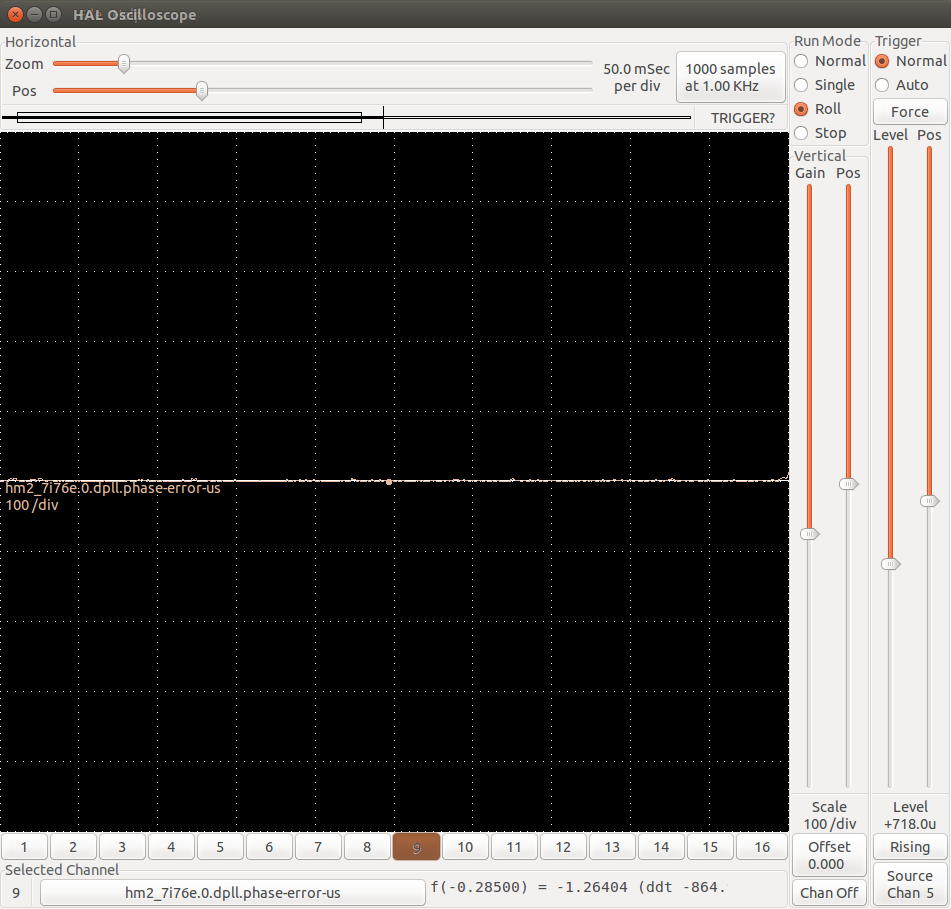

I ask because your DPLL error plot even when adjusted, looks quite bad for a PCI system

For example here is a Ethernet system which should typically have worse latency but is much much better

than your system:

If i get a chance i will try and duplicate your issue here later today and see if I can come up with a workaround

What kind of latency do you get on that system?

I ask because your DPLL error plot even when adjusted, looks quite bad for a PCI system

For example here is a Ethernet system which should typically have worse latency but is much much better

than your system:

If i get a chance i will try and duplicate your issue here later today and see if I can come up with a workaround

Please Log in or Create an account to join the conversation.

- PCW

-

- Offline

- Moderator

-

Less

More

- Posts: 17877

- Thank you received: 5236

28 Oct 2016 01:50 #82162

by PCW

Replied by PCW on topic SSI absolute encoders and analog servos

I did some testing and the standard DPLL has a lock-in range of about +-0.75% at 1 KHz

normally this is OK but the PCI clock is just about that far off on your Motherboard

I made a quick test with variant DPLL tuning that allows about a 3% lock in range

so if you remind me what bitfile name you have, i can make a wide lock-in range version

for you to test. The variant also incorporates a integral term in the DPLL so small timebase offsets

are zeroed

normally this is OK but the PCI clock is just about that far off on your Motherboard

I made a quick test with variant DPLL tuning that allows about a 3% lock in range

so if you remind me what bitfile name you have, i can make a wide lock-in range version

for you to test. The variant also incorporates a integral term in the DPLL so small timebase offsets

are zeroed

Please Log in or Create an account to join the conversation.

Moderators: PCW, jmelson

Time to create page: 0.121 seconds