Create a FPGA board for raspberry

- Boaschti

- Offline

- Junior Member

-

Less

More

- Posts: 23

- Thank you received: 2

04 Dec 2021 11:24 #228341

by Boaschti

Create a FPGA board for raspberry was created by Boaschti

Hello, i plan to create a custom I/O like the mesa 7c80. My problem is that mesa cards are not available at this time and i need relais on board.

We have much experience with electronics.

Now i have seen the post from gtt38 Link with a running fpga eval board and a raspberry.

My questions are:

Are there any layouts available with a fpga and raspberry?

When using the fpga board Link :

Are there any more informations about using universal FPGA Boards?

Do i need any modifikations in hostmot2 firmware?

Do i need any modifikations on the eval board?

Are there any showbreakers which i don't know yet (like closed sources or unknown code or fpga firmware modifications)? (Except normal showbreakers with electronic components...)

Best regards.

We have much experience with electronics.

Now i have seen the post from gtt38 Link with a running fpga eval board and a raspberry.

My questions are:

Are there any layouts available with a fpga and raspberry?

When using the fpga board Link :

Are there any more informations about using universal FPGA Boards?

Do i need any modifikations in hostmot2 firmware?

Do i need any modifikations on the eval board?

Are there any showbreakers which i don't know yet (like closed sources or unknown code or fpga firmware modifications)? (Except normal showbreakers with electronic components...)

Best regards.

Please Log in or Create an account to join the conversation.

- Henk

- Offline

- Platinum Member

-

Less

More

- Posts: 407

- Thank you received: 92

04 Dec 2021 15:18 #228346

by Henk

Replied by Henk on topic Create a FPGA board for raspberry

This came up recently. Looks interesting.

Please Log in or Create an account to join the conversation.

- Bari

-

- Offline

- Platinum Member

-

Less

More

- Posts: 639

- Thank you received: 234

15 Dec 2021 05:53 #229097

by Bari

Replied by Bari on topic Create a FPGA board for raspberry

forum.linuxcnc.org/27-driver-boards/44422-colorcnc

"ColorCNC" because it's a firmware driver for Chinese board Colorlight 5A-75B

www.colorlightinside.com/Products/i%20Re...ng-series/34_25.html

Sells for ~$15

"ColorCNC" because it's a firmware driver for Chinese board Colorlight 5A-75B

www.colorlightinside.com/Products/i%20Re...ng-series/34_25.html

Sells for ~$15

Please Log in or Create an account to join the conversation.

- Boaschti

- Offline

- Junior Member

-

Less

More

- Posts: 23

- Thank you received: 2

19 Jan 2022 20:06 - 19 Jan 2022 20:11 #232477

by Boaschti

Replied by Boaschti on topic Create a FPGA board for raspberry

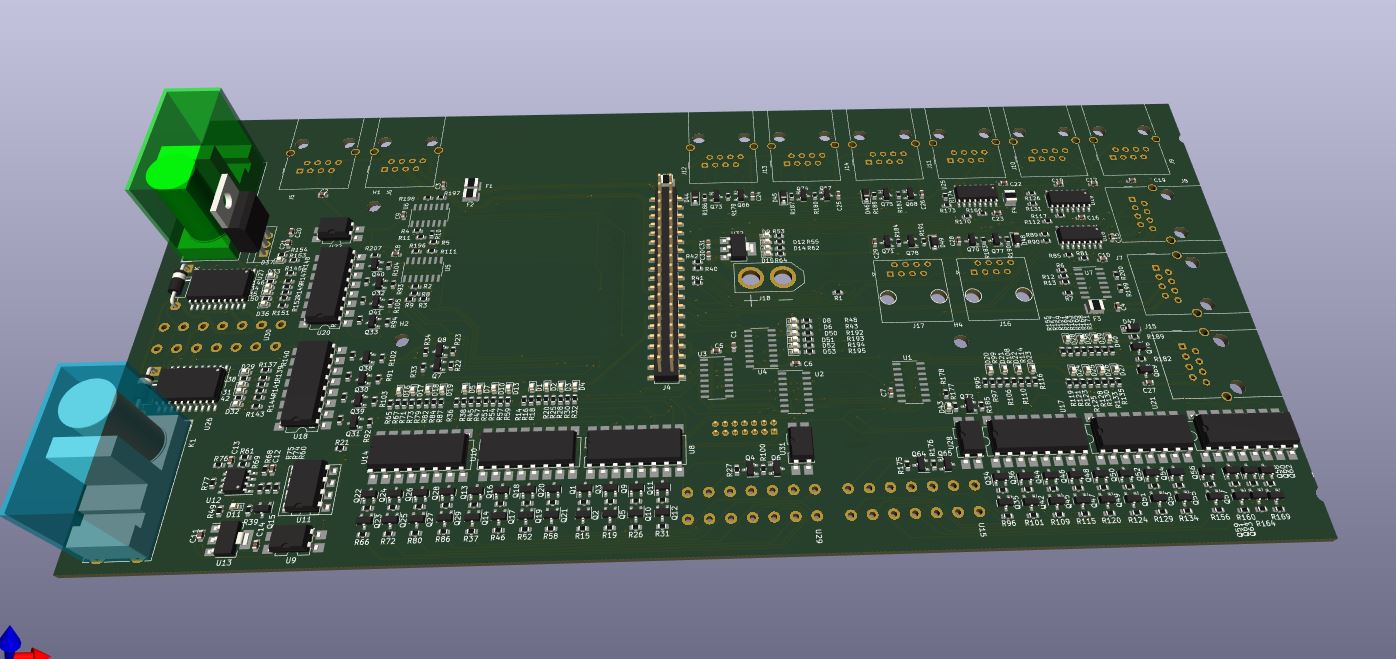

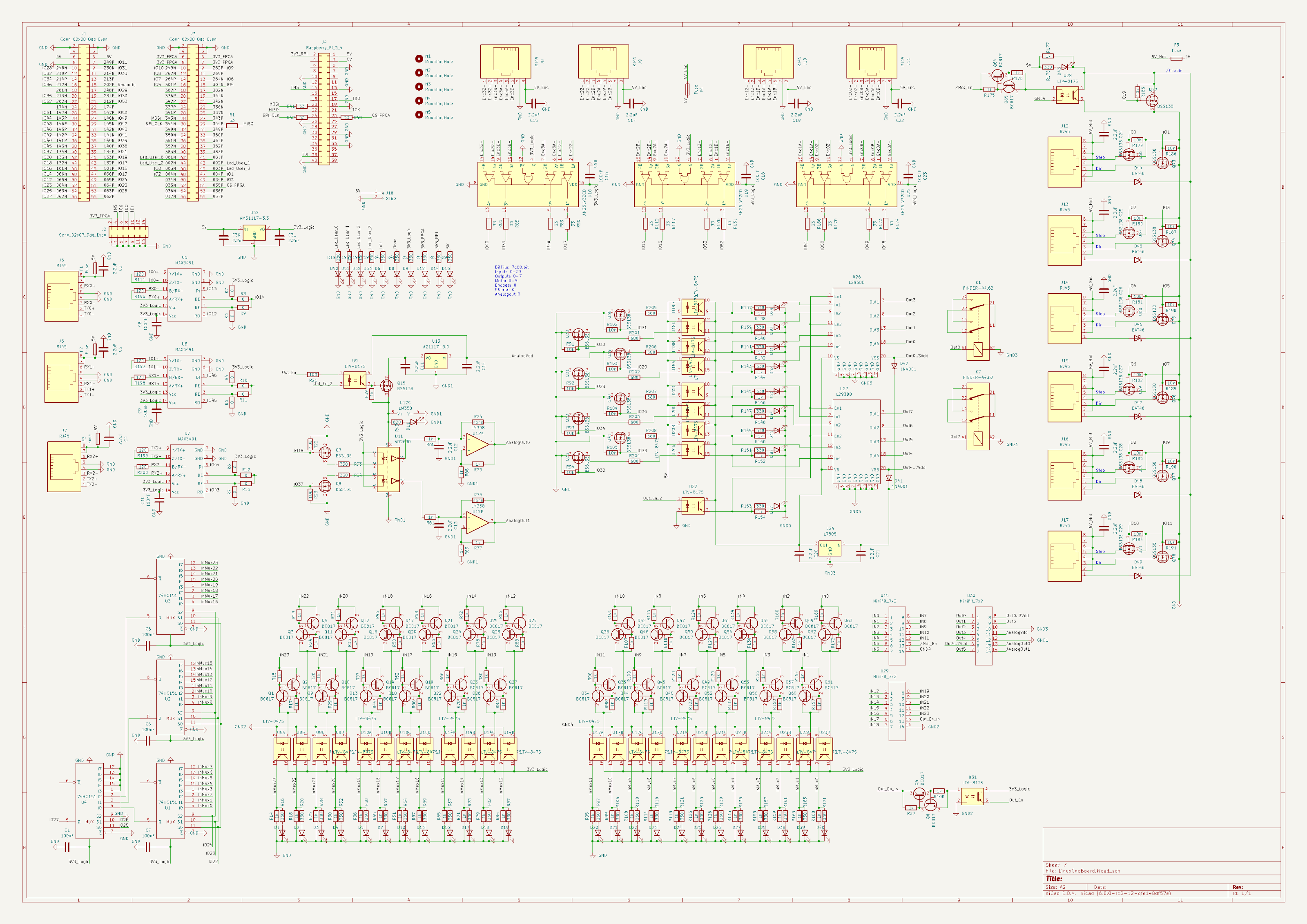

Is it possible to make a custom .bit File with following IO pinout. Of course without having trouble with FPGA stability.

The basic pinout is form 7c80 board and i need some extensions.

See attachment for or

The basic pinout is form 7c80 board and i need some extensions.

Configuration pin-out:

IO Connections for StepGens+Misc

Pin# I/O Pri. func Sec. func Chan Pin func Pin Dir

0 0 IOPort StepGen 0 Step/Table1 (Out)

0 1 IOPort StepGen 0 Dir/Table2 (Out)

0 2 IOPort StepGen 1 Step/Table1 (Out)

0 3 IOPort StepGen 1 Dir/Table2 (Out)

0 4 IOPort StepGen 2 Step/Table1 (Out)

0 5 IOPort StepGen 2 Dir/Table2 (Out)

0 6 IOPort StepGen 3 Step/Table1 (Out)

0 7 IOPort StepGen 3 Dir/Table2 (Out)

0 8 IOPort StepGen 4 Step/Table1 (Out)

0 9 IOPort StepGen 4 Dir/Table2 (Out)

0 10 IOPort StepGen 5 Step/Table1 (Out)

0 11 IOPort StepGen 5 Dir/Table2 (Out)

0 12 IOPort SSerial 0 RXData0 (In)

0 13 IOPort SSerial 0 TXData0 (Out)

0 14 IOPort SSerial 0 TXEn0 (Out)

0 15 IOPort QCount 0 Quad-A (In)

0 16 IOPort QCount 0 Quad-B (In)

0 17 IOPort QCount 0 Quad-IDX (In)

0 18 IOPort PWM 0 PWM (Out)

0 19 IOPort PWM 0 /Enable (Out)

0 20 IOPort None

0 21 IOPort None

0 22 IOPort InMux 0 Addr0 (Out)

0 23 IOPort InMux 0 Addr1 (Out)

0 24 IOPort InMux 0 Addr2 (Out)

0 25 IOPort InMux 0 Addr3 (Out)

0 26 IOPort InMux 0 Addr4 (Out)

IO Connections for Outputs+P1

Pin# I/O Pri. func Sec. func Chan Pin func Pin Dir

0 27 IOPort InMux 0 Data0 (In)

0 28 IOPort SSR 0 Out-00 (Out)

0 29 IOPort SSR 0 Out-01 (Out)

0 30 IOPort SSR 0 Out-02 (Out)

0 31 IOPort SSR 0 Out-03 (Out)

0 32 IOPort SSR 0 Out-04 (Out)

0 33 IOPort SSR 0 Out-05 (Out)

0 34 IOPort SSR 0 Out-06 (Out)

0 35 IOPort SSR 0 Out-07 (Out)

0 36 IOPort SSR 0 AC Ref (Out)

0 37 IOPort PWM 1 PWM (Out)

0 38 IOPort QCount 1 Quad-A (In)

0 39 IOPort QCount 1 Quad-B (In)

0 40 IOPort QCount 1 Quad-IDX (In)

0 41 IOPort None

0 42 IOPort None

0 43 IOPort SSerial 0 RXData2 (In)

0 44 IOPort SSerial 0 TXData2 (Out)

0 45 IOPort SSerial 0 RXData1 (In)

0 46 IOPort SSerial 0 TXData1 (Out)

0 47 IOPort None

0 48 IOPort QCount 2 Quad-A (In)

0 49 IOPort QCount 2 Quad-B (In)

0 50 IOPort QCount 2 Quad-IDX (In)

0 51 IOPort QCount 3 Quad-A (In)

0 52 IOPort QCount 3 Quad-B (In)

0 53 IOPort QCount 3 Quad-IDX (In)See attachment for or

Attachments:

Last edit: 19 Jan 2022 20:11 by Boaschti.

The following user(s) said Thank You: besriworld

Please Log in or Create an account to join the conversation.

- PCW

-

- Offline

- Moderator

-

Less

More

- Posts: 17864

- Thank you received: 5231

19 Jan 2022 22:28 - 19 Jan 2022 22:30 #232488

by PCW

Replied by PCW on topic Create a FPGA board for raspberry

A custom bitfile needs at least

The FPGA pinout (which pin goes to which GPIO bit/interface bit etc)

The I/O pinout (Which GPIO bit has which secondary function)

Note that you probably don't want to to use SSR modules unless you are using transformer isolation

The FPGA pinout (which pin goes to which GPIO bit/interface bit etc)

The I/O pinout (Which GPIO bit has which secondary function)

Note that you probably don't want to to use SSR modules unless you are using transformer isolation

Last edit: 19 Jan 2022 22:30 by PCW.

Please Log in or Create an account to join the conversation.

- Boaschti

- Offline

- Junior Member

-

Less

More

- Posts: 23

- Thank you received: 2

20 Jan 2022 08:42 #232501

by Boaschti

Replied by Boaschti on topic Create a FPGA board for raspberry

I want to use the fpga pinout from the 7c80.

What i have to use instead of ssr funktionality? I need simple outputs for air, water, vacuum, ligths, spindle (kress/amb).

What is the exactly funktionality of IO19...PWM.../ENABLE? Is it used to controll enable input of steppers/servos or is it used to disable pwmoutputs?

What i have to use instead of ssr funktionality? I need simple outputs for air, water, vacuum, ligths, spindle (kress/amb).

What is the exactly funktionality of IO19...PWM.../ENABLE? Is it used to controll enable input of steppers/servos or is it used to disable pwmoutputs?

Please Log in or Create an account to join the conversation.

- D.L.

- Offline

- Senior Member

-

Less

More

- Posts: 55

- Thank you received: 37

20 Jan 2022 11:50 #232513

by D.L.

Replied by D.L. on topic Create a FPGA board for raspberry

No sense to use multiplexers for expand inputs, xc6slx9 in spi hostmot2 configuration support up to 85 gpio pins(for example: 4 port x 21 pin or 5 port x 17 pin).

Please Log in or Create an account to join the conversation.

- Boaschti

- Offline

- Junior Member

-

Less

More

- Posts: 23

- Thank you received: 2

20 Jan 2022 18:58 - 20 Jan 2022 19:10 #232545

by Boaschti

Replied by Boaschti on topic Create a FPGA board for raspberry

Ok. Thats a interesting info.

My idea was to design the hardware very similar to the 7c80 board (IO0..IO36). There is already a bitfile for this and as a linuxcnc beginner I have fewer sources of error. So I can start more easy.

In future i want to have a bitfile for IO00..IO53. My machine doesn't has a encoder at this moment but it is planed.

But if I have to make a bitfile because of the ssr functionality then I can also remove the multiplexer.

My idea was to design the hardware very similar to the 7c80 board (IO0..IO36). There is already a bitfile for this and as a linuxcnc beginner I have fewer sources of error. So I can start more easy.

In future i want to have a bitfile for IO00..IO53. My machine doesn't has a encoder at this moment but it is planed.

But if I have to make a bitfile because of the ssr functionality then I can also remove the multiplexer.

Last edit: 20 Jan 2022 19:10 by Boaschti.

Please Log in or Create an account to join the conversation.

- D.L.

- Offline

- Senior Member

-

Less

More

- Posts: 55

- Thank you received: 37

20 Jan 2022 19:23 #232548

by D.L.

Replied by D.L. on topic Create a FPGA board for raspberry

Before loading the firmware - all pins in high impedance state.

After loading the firmware - all pins in gpio mode.

After loading the LinuxCNC, pins may be switching to the secondary function - it defined in hal/ini config string.

If in config string defined num_ssrs=0, all ssr pins in gpio mode.

After loading the firmware - all pins in gpio mode.

After loading the LinuxCNC, pins may be switching to the secondary function - it defined in hal/ini config string.

If in config string defined num_ssrs=0, all ssr pins in gpio mode.

Please Log in or Create an account to join the conversation.

- Boaschti

- Offline

- Junior Member

-

Less

More

- Posts: 23

- Thank you received: 2

13 Feb 2022 12:40 #234691

by Boaschti

Replied by Boaschti on topic Create a FPGA board for raspberry

Attachments:

Please Log in or Create an account to join the conversation.

Moderators: PCW, jmelson

Time to create page: 0.155 seconds