- Hardware & Machines

- Driver Boards

- [Solved]How to enable/check MESA 7i96s with 7i76 daughter board - problem??

[Solved]How to enable/check MESA 7i96s with 7i76 daughter board - problem??

- camb0

- Offline

- Senior Member

-

Less

More

- Posts: 61

- Thank you received: 9

16 Jun 2023 09:45 - 17 Jun 2023 07:00 #273687

by camb0

[Solved]How to enable/check MESA 7i96s with 7i76 daughter board - problem?? was created by camb0

Last edit: 17 Jun 2023 07:00 by camb0. Reason: Solved status

Please Log in or Create an account to join the conversation.

- PCW

-

- Offline

- Moderator

-

Less

More

- Posts: 17847

- Thank you received: 5226

16 Jun 2023 12:56 #273693

by PCW

Replied by PCW on topic How to enable/check MESA 7i96s with 7i76 daughter board - Cable/config problem??

The sserial ports on the 7I76 are channels 1 (Field I/O) and 2 (7I76 sserial expansion)

so sserial_port_0=020 (if you want mode 2 on the 7I76 field I/O section)

so sserial_port_0=020 (if you want mode 2 on the 7I76 field I/O section)

Please Log in or Create an account to join the conversation.

- camb0

- Offline

- Senior Member

-

Less

More

- Posts: 61

- Thank you received: 9

16 Jun 2023 22:06 - 16 Jun 2023 22:07 #273720

by camb0

Replied by camb0 on topic How to enable/check MESA 7i96s with 7i76 daughter board - Cable/config problem??

Thx for the explanation of the sserial_port it's really useful, however I probably should have phrased the question better. I can't see the 7i76, hence I was looking at the sserial_port setting as something that might be preventing me from seeing it.

My intent is to use the 7i76 for additional IO as I don't have enough ports on the 7i96 for limit switches + tool changer + other items. From the manual and your message it looks like I should be setting it up for mode 1 (all IO plus the analog ports). So that would be a config string of:

halcmd: loadrt hm2_eth board_ip="10.10.10.10" config="sserial_port_0=010"

This issue I have is that when I do that I only see 51 pins which I'm pretty sure is just the 7i96s as per below. Any other hints as to what mistake/omission/tests I can do to verify I've got it setup correctly?

My intent is to use the 7i76 for additional IO as I don't have enough ports on the 7i96 for limit switches + tool changer + other items. From the manual and your message it looks like I should be setting it up for mode 1 (all IO plus the analog ports). So that would be a config string of:

halcmd: loadrt hm2_eth board_ip="10.10.10.10" config="sserial_port_0=010"

This issue I have is that when I do that I only see 51 pins which I'm pretty sure is just the 7i96s as per below. Any other hints as to what mistake/omission/tests I can do to verify I've got it setup correctly?

halcmd: loadrt hm2_eth board_ip="10.10.10.10" config="sserial_port_0=010"

hm2_eth: loading Mesa AnyIO HostMot2 ethernet driver version 0.2

hm2_eth: 10.10.10.10: INFO: Hardware address (MAC): 00:60:1b:16:86:5e

hm2_eth: discovered 7I96S

hm2/hm2_7i96s.0: Low Level init 0.15

hm2/hm2_7i96s.0: Smart Serial Firmware Version 43

hm2/hm2_7i96s.0: 51 I/O Pins used:

hm2/hm2_7i96s.0: IO Pin 000 (TB3-01): InM Input Module #0, pin in0 (Input).....

Last edit: 16 Jun 2023 22:07 by camb0. Reason: formatting

Please Log in or Create an account to join the conversation.

- PCW

-

- Offline

- Moderator

-

Less

More

- Posts: 17847

- Thank you received: 5226

16 Jun 2023 22:52 #273722

by PCW

Replied by PCW on topic How to enable/check MESA 7i96s with 7i76 daughter board - Cable/config problem??

The reason I mentioned the sserial_port_0 is that your original example would have disabled the 7I76.

The 7I76 is still not being detected

So it may be cabling or power

So you have both 5V and field power?

7I76 W1 and W3 Left?

Here is what I get running a 7I96S+7I76 with 7i96s_7i76d.bin firmware:

The 7I76 is still not being detected

So it may be cabling or power

So you have both 5V and field power?

7I76 W1 and W3 Left?

Here is what I get running a 7I96S+7I76 with 7i96s_7i76d.bin firmware:

Attachments:

Please Log in or Create an account to join the conversation.

- camb0

- Offline

- Senior Member

-

Less

More

- Posts: 61

- Thank you received: 9

16 Jun 2023 23:20 #273724

by camb0

Replied by camb0 on topic How to enable/check MESA 7i96s with 7i76 daughter board - Cable/config problem??

Thx, I’m suspicious of the cable.

I’ve tested it with power to the board and power via the db25 cable (swapping the jumpers to suit), both times the LED’s were on and green.

I’ll double check the jumpers when I get home.

I’ve got power to the field (24v).

I’ve tested it with power to the board and power via the db25 cable (swapping the jumpers to suit), both times the LED’s were on and green.

I’ll double check the jumpers when I get home.

I’ve got power to the field (24v).

Please Log in or Create an account to join the conversation.

- camb0

- Offline

- Senior Member

-

Less

More

- Posts: 61

- Thank you received: 9

17 Jun 2023 00:37 #273728

by camb0

Replied by camb0 on topic How to enable/check MESA 7i96s with 7i76 daughter board - Cable/config problem??

With logic power coming via the DB25 (5v) and field power via TB1 (24v) I've got:

W1 = right (VIN SEP)

W2 = left (5v FPGA)

W3 = left

W1 = right (VIN SEP)

W2 = left (5v FPGA)

W3 = left

Please Log in or Create an account to join the conversation.

- camb0

- Offline

- Senior Member

-

Less

More

- Posts: 61

- Thank you received: 9

17 Jun 2023 01:00 #273729

by camb0

Replied by camb0 on topic How to enable/check MESA 7i96s with 7i76 daughter board - Cable/config problem??

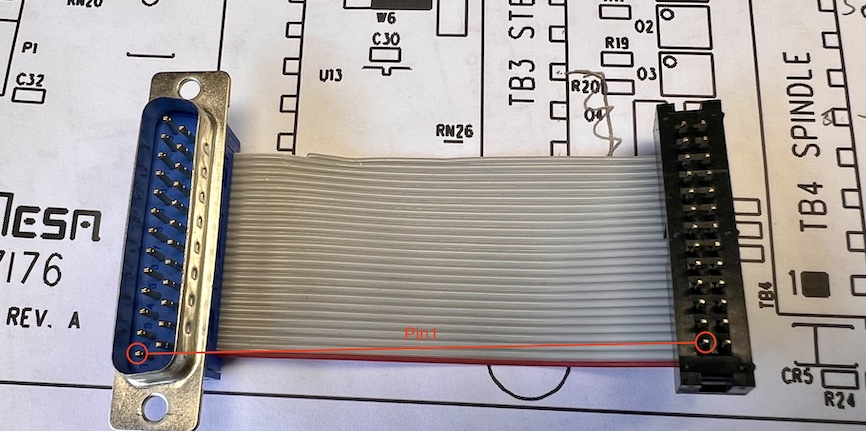

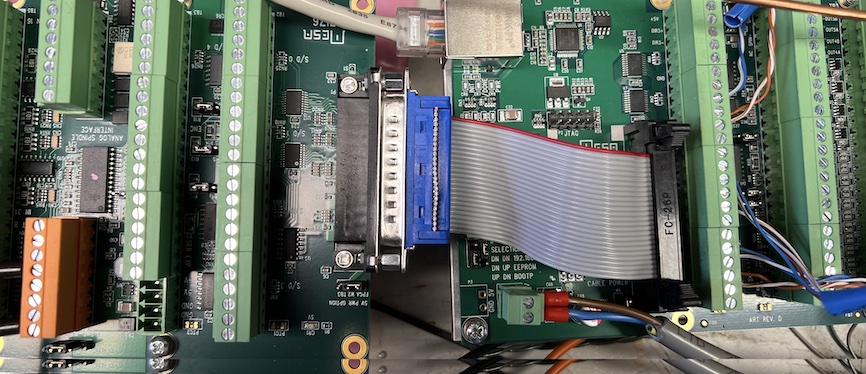

I've bench tested the continuity of the pins with my volt meter, they're all connected.

I've checked pin 1 against the diagrams and I think I've got it correct but I might have misread it.

Here's a pic of the cable with pin 1's aligned (note the 26pin end has a socket on it to make it easier to test) the 26 pin locating boss is on the left (first pic).

Last pic is of the cable installed.

I've checked pin 1 against the diagrams and I think I've got it correct but I might have misread it.

Here's a pic of the cable with pin 1's aligned (note the 26pin end has a socket on it to make it easier to test) the 26 pin locating boss is on the left (first pic).

Last pic is of the cable installed.

Attachments:

Please Log in or Create an account to join the conversation.

- PCW

-

- Offline

- Moderator

-

Less

More

- Posts: 17847

- Thank you received: 5226

17 Jun 2023 02:47 #273730

by PCW

Replied by PCW on topic How to enable/check MESA 7i96s with 7i76 daughter board - Cable/config problem??

W1 must be in the left position

The following user(s) said Thank You: camb0

Please Log in or Create an account to join the conversation.

- camb0

- Offline

- Senior Member

-

Less

More

- Posts: 61

- Thank you received: 9

17 Jun 2023 05:15 #273733

by camb0

Replied by camb0 on topic How to enable/check MESA 7i96s with 7i76 daughter board - Cable/config problem??

Yahtzee!!!!

I see the 7i76 now, thx a bunch for your assistance and patience.

I see the 7i76 now, thx a bunch for your assistance and patience.

The following user(s) said Thank You: tommylight

Please Log in or Create an account to join the conversation.

- Boogie

- Offline

- Premium Member

-

Less

More

- Posts: 97

- Thank you received: 9

22 Feb 2025 19:29 #322295

by Boogie

Replied by Boogie on topic How to enable/check MESA 7i96s with 7i76 daughter board - Cable/config problem??

Was W1 position the issue?

Please Log in or Create an account to join the conversation.

Moderators: PCW, jmelson

- Hardware & Machines

- Driver Boards

- [Solved]How to enable/check MESA 7i96s with 7i76 daughter board - problem??

Time to create page: 0.691 seconds