Bitfile for 6i25+7i74+7i85

- ChironFZ16

-

Topic Author

Topic Author

- Offline

- Senior Member

-

- Posts: 58

- Thank you received: 12

Please Log in or Create an account to join the conversation.

- PCW

-

- Offline

- Moderator

-

- Posts: 17847

- Thank you received: 5226

Please Log in or Create an account to join the conversation.

- PCW

-

- Offline

- Moderator

-

- Posts: 17847

- Thank you received: 5226

That would normally end up with 4 encoders and 13 sserial

channels, and no PWM or stepgens. Is this what you intended?

Please Log in or Create an account to join the conversation.

- tommylight

-

- Offline

- Moderator

-

- Posts: 21505

- Thank you received: 7331

I was wondering the same thing.Its a bit of an odd configuration. is It the really a 7I85 + 7I74?

Please Log in or Create an account to join the conversation.

- ChironFZ16

-

Topic Author

Topic Author

- Offline

- Senior Member

-

- Posts: 58

- Thank you received: 12

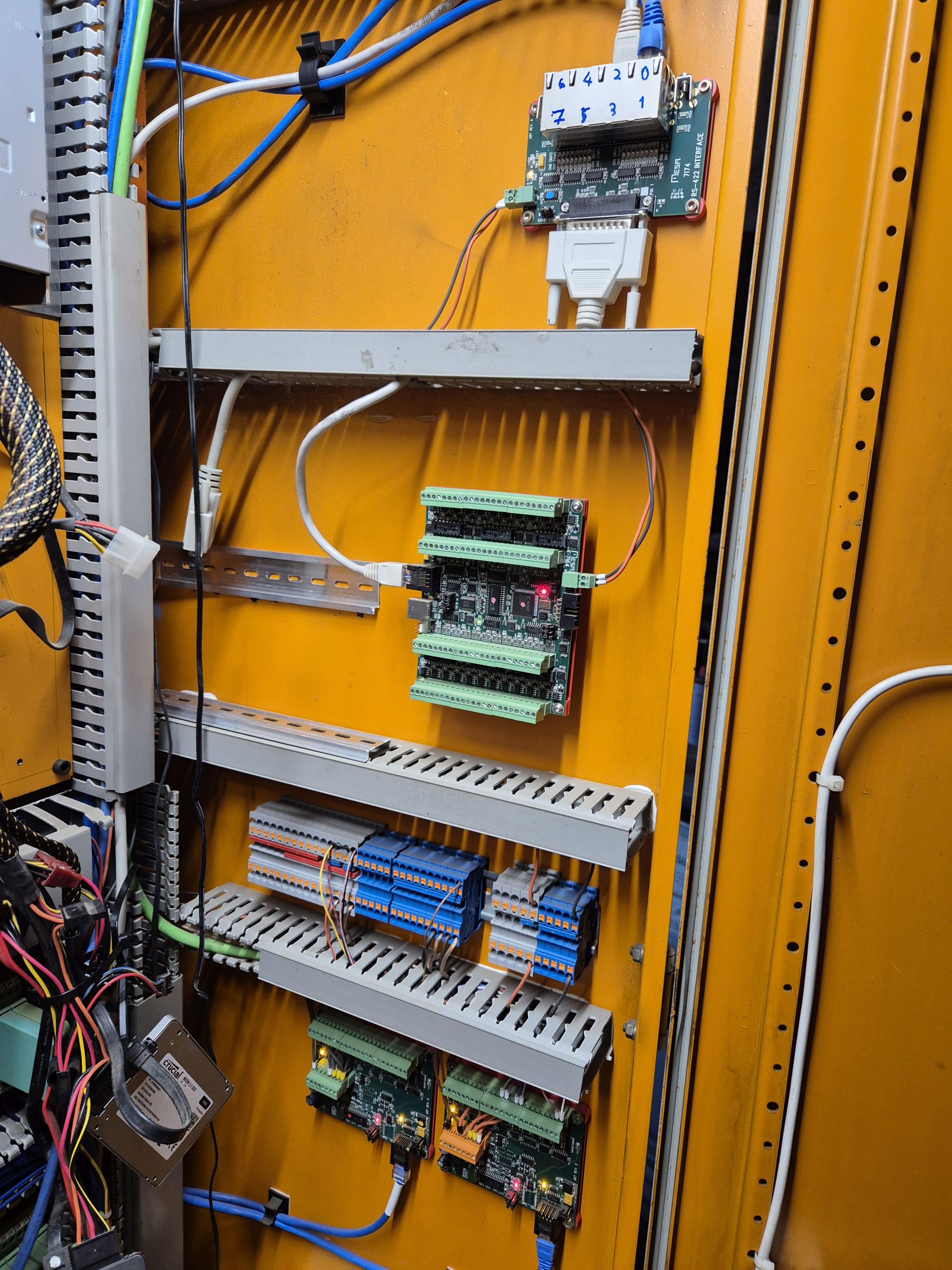

Attachments:

Please Log in or Create an account to join the conversation.

- PCW

-

- Offline

- Moderator

-

- Posts: 17847

- Thank you received: 5226

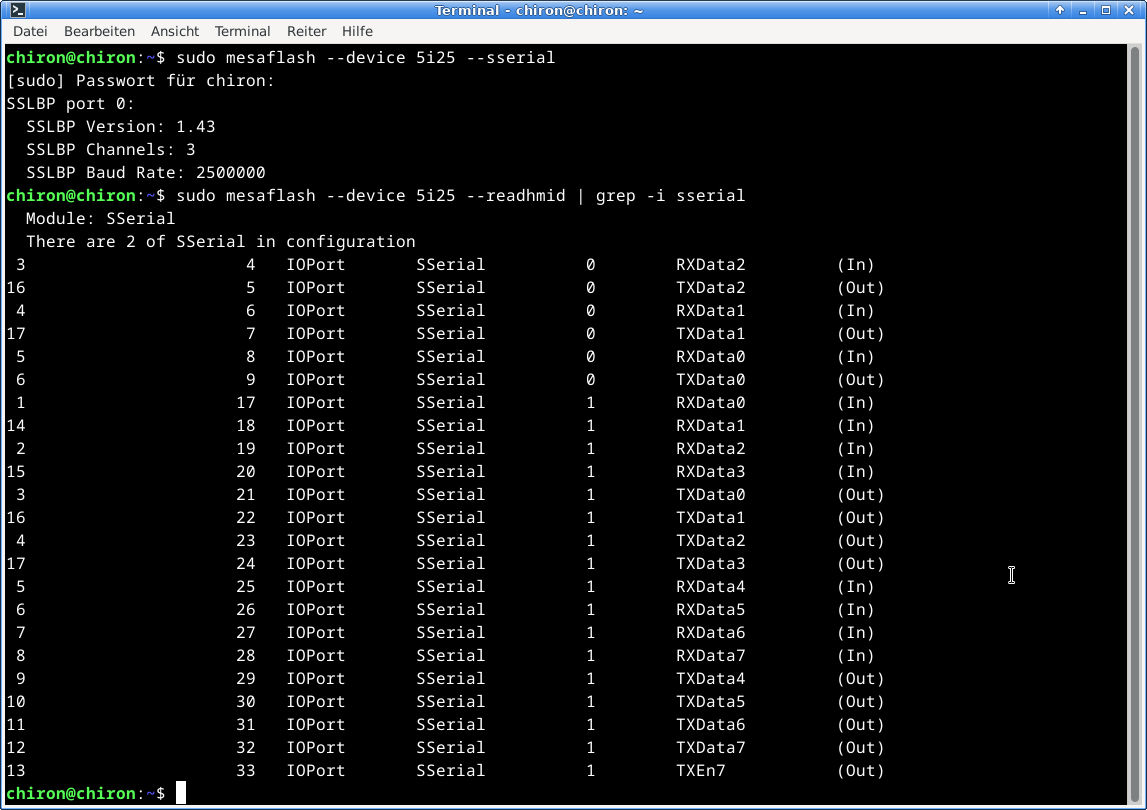

5I25/6I25 config for 7I85 on P3 (ext DB25), 7I74 on P2 (internal header)

Only 3 sserial channels on the 7I85 (port 0) because of space considerations

All 8 sserial channels on port 1 (7I74)

Attachments:

Please Log in or Create an account to join the conversation.

- ChironFZ16

-

Topic Author

Topic Author

- Offline

- Senior Member

-

- Posts: 58

- Thank you received: 12

The old config :

[HOSTMOT2]

DRIVER=hm2_pci

BOARD=5i20

CONFIG="num_encoders=0 num_stepgens=0 sserial_port_1=021xxx,firmware=hm2/5i20/svst6_6_7i48.bit num_encoders=6 num_pwmgens=6 num_stepgens=0num_leds=0,firmware=hm2/5i20/svst6_6_7i48.bit num_encoders=0 num_pwmgens=0 num_stepgens=0num_leds=0"

[MACROS]

Old config:

Old config:

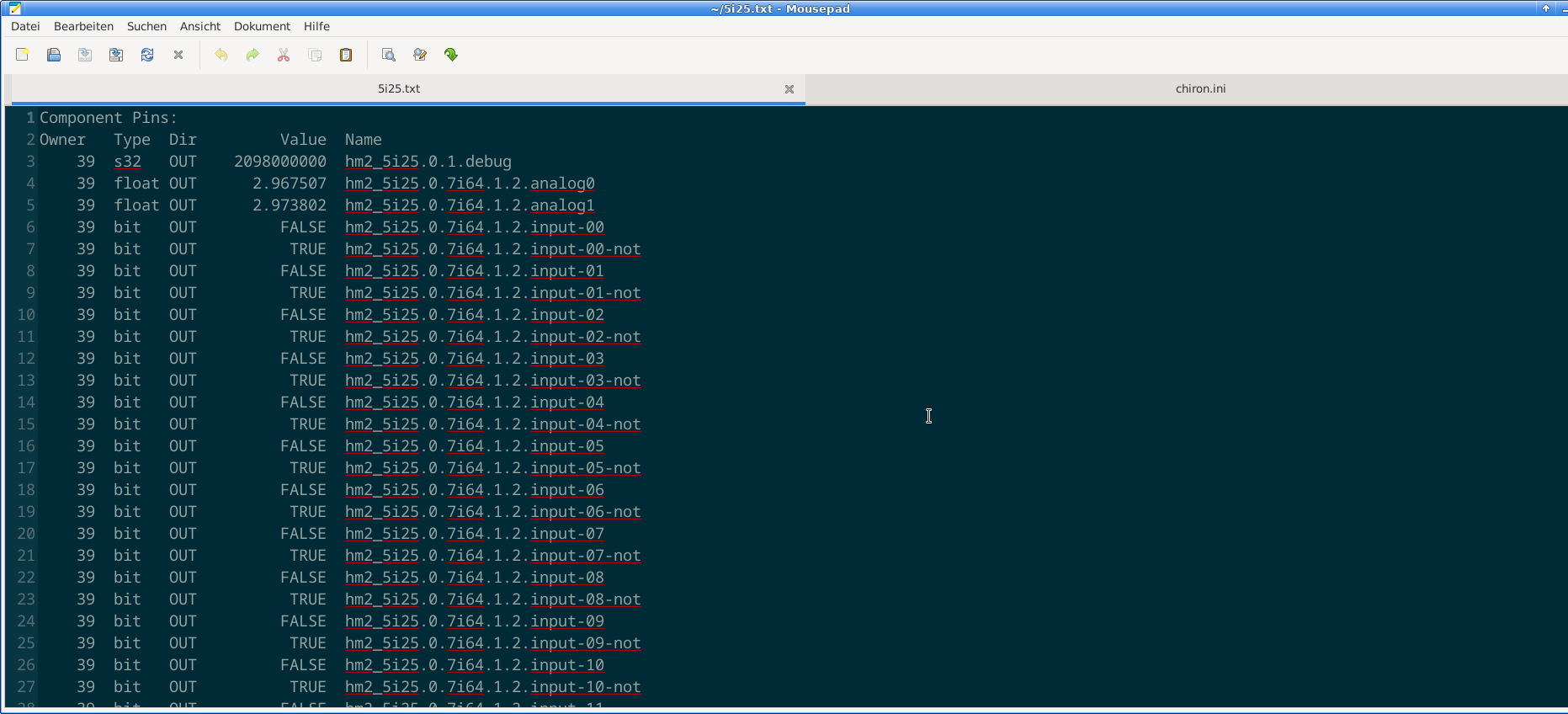

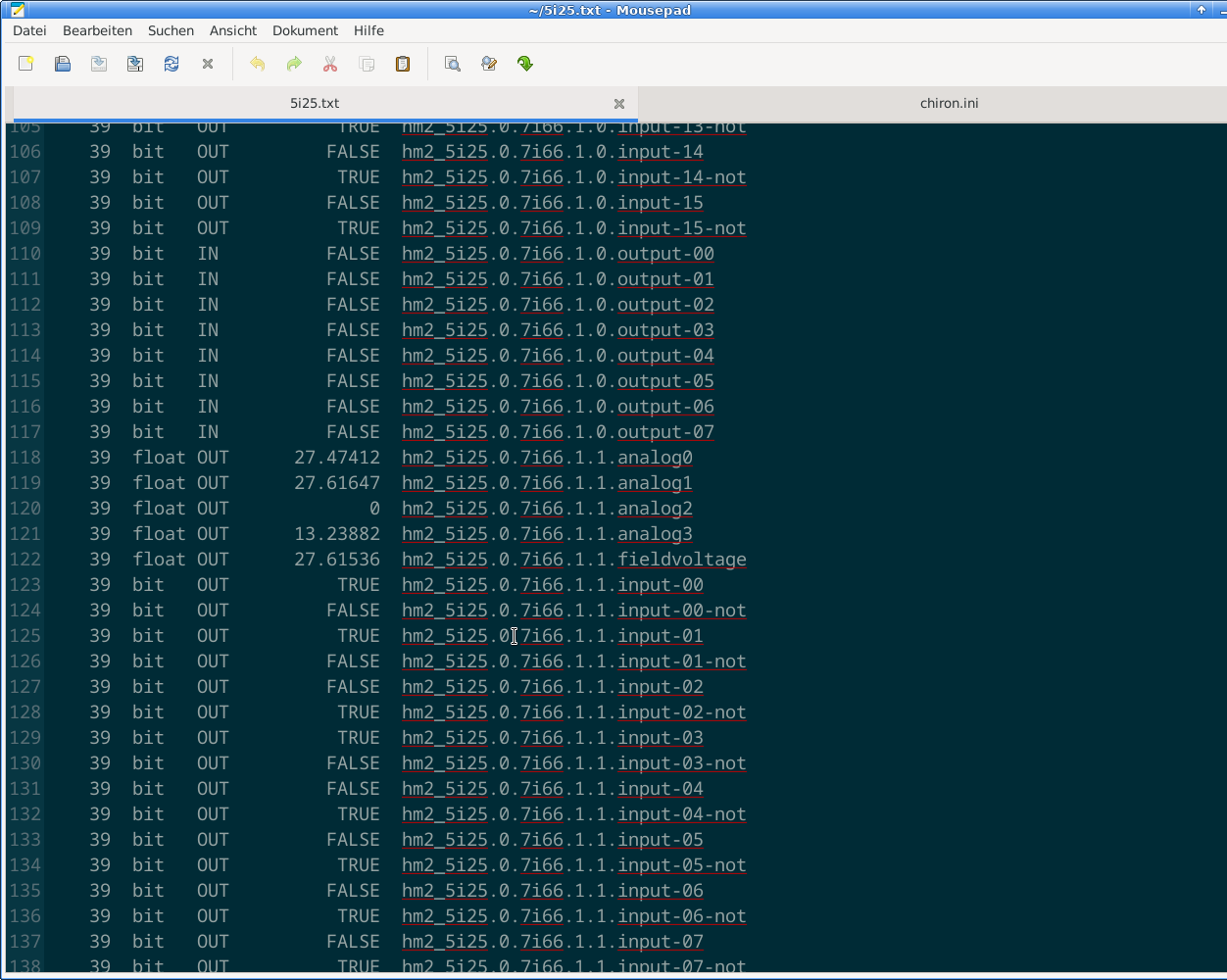

MesaCT:

Read HMID

Returned: Success

Configuration Name: HOSTMOT2

General configuration information:

BoardName : MESA5I25

FPGA Size: 9 KGates

FPGA Pins: 144

Number of IO Ports: 2

Width of one I/O port: 17

Clock Low frequency: 33.3333 MHz

Clock High frequency: 200.0000 MHz

IDROM Type: 3

Instance Stride 0: 4

Instance Stride 1: 64

Register Stride 0: 256

Register Stride 1: 256

Modules in configuration:

Module: DPLL

There are 1 of DPLL in configuration

Version: 0

Registers: 7

BaseAddress: 7000

ClockFrequency: 33.333 MHz

Register Stride: 256 bytes

Instance Stride: 4 bytes

Module: WatchDog

There are 1 of WatchDog in configuration

Version: 0

Registers: 3

BaseAddress: 0C00

ClockFrequency: 33.333 MHz

Register Stride: 256 bytes

Instance Stride: 4 bytes

Module: IOPort

There are 2 of IOPort in configuration

Version: 0

Registers: 5

BaseAddress: 1000

ClockFrequency: 33.333 MHz

Register Stride: 256 bytes

Instance Stride: 4 bytes

Module: MuxedQCount

There are 4 of MuxedQCount in configuration

Version: 4

Registers: 5

BaseAddress: 3600

ClockFrequency: 33.333 MHz

Register Stride: 256 bytes

Instance Stride: 4 bytes

Module: MuxedQCountSel

There are 1 of MuxedQCountSel in configuration

Version: 0

Registers: 0

BaseAddress: 0000

ClockFrequency: 33.333 MHz

Register Stride: 256 bytes

Instance Stride: 4 bytes

Module: SSerial

There are 2 of SSerial in configuration

Version: 0

Registers: 6

BaseAddress: 5B00

ClockFrequency: 33.333 MHz

Register Stride: 256 bytes

Instance Stride: 64 bytes

Module: LED

There are 1 of LED in configuration

Version: 0

Registers: 1

BaseAddress: 0200

ClockFrequency: 33.333 MHz

Register Stride: 256 bytes

Instance Stride: 4 bytes

Configuration pin-out:

IO Connections for P3

DB25 pin# I/O Pri. func Sec. func Chan Sec. Pin func Sec. Pin Dir

1 0 IOPort None

14 1 IOPort None

2 2 IOPort None

15 3 IOPort None

3 4 IOPort SSerial 0 RXData2 (In)

16 5 IOPort SSerial 0 TXData2 (Out)

4 6 IOPort SSerial 0 RXData1 (In)

17 7 IOPort SSerial 0 TXData1 (Out)

5 8 IOPort SSerial 0 RXData0 (In)

6 9 IOPort SSerial 0 TXData0 (Out)

7 10 IOPort MuxedQCountSel 0 MuxSel0 (Out)

8 11 IOPort MuxedQCount 0 MuxQ-A (In)

9 12 IOPort MuxedQCount 0 MuxQ-B (In)

10 13 IOPort MuxedQCount 0 MuxQ-IDX (In)

11 14 IOPort MuxedQCount 1 MuxQ-A (In)

12 15 IOPort MuxedQCount 1 MuxQ-B (In)

13 16 IOPort MuxedQCount 1 MuxQ-IDX (In)

IO Connections for P2

DB25 pin# I/O Pri. func Sec. func Chan Sec. Pin func Sec. Pin Dir

1 17 IOPort SSerial 1 RXData0 (In)

14 18 IOPort SSerial 1 RXData1 (In)

2 19 IOPort SSerial 1 RXData2 (In)

15 20 IOPort SSerial 1 RXData3 (In)

3 21 IOPort SSerial 1 TXData0 (Out)

16 22 IOPort SSerial 1 TXData1 (Out)

4 23 IOPort SSerial 1 TXData2 (Out)

17 24 IOPort SSerial 1 TXData3 (Out)

5 25 IOPort SSerial 1 RXData4 (In)

6 26 IOPort SSerial 1 RXData5 (In)

7 27 IOPort SSerial 1 RXData6 (In)

8 28 IOPort SSerial 1 RXData7 (In)

9 29 IOPort SSerial 1 TXData4 (Out)

10 30 IOPort SSerial 1 TXData5 (Out)

11 31 IOPort SSerial 1 TXData6 (Out)

12 32 IOPort SSerial 1 TXData7 (Out)

13 33 IOPort SSerial 1 TXEn7 (Out)

Attachments:

Please Log in or Create an account to join the conversation.

- PCW

-

- Offline

- Moderator

-

- Posts: 17847

- Thank you received: 5226

That is, what changed?

Please Log in or Create an account to join the conversation.

- ChironFZ16

-

Topic Author

Topic Author

- Offline

- Senior Member

-

- Posts: 58

- Thank you received: 12

Please Log in or Create an account to join the conversation.

- PCW

-

- Offline

- Moderator

-

- Posts: 17847

- Thank you received: 5226

Maybe there's some meta-problem of some kind.

Please Log in or Create an account to join the conversation.