Mesa 7i90 in SPI mode

- kaklik

- Offline

- New Member

-

Less

More

- Posts: 15

- Thank you received: 0

29 Mar 2016 12:38 #72318

by kaklik

Replied by kaklik on topic Mesa 7i90 in SPI mode

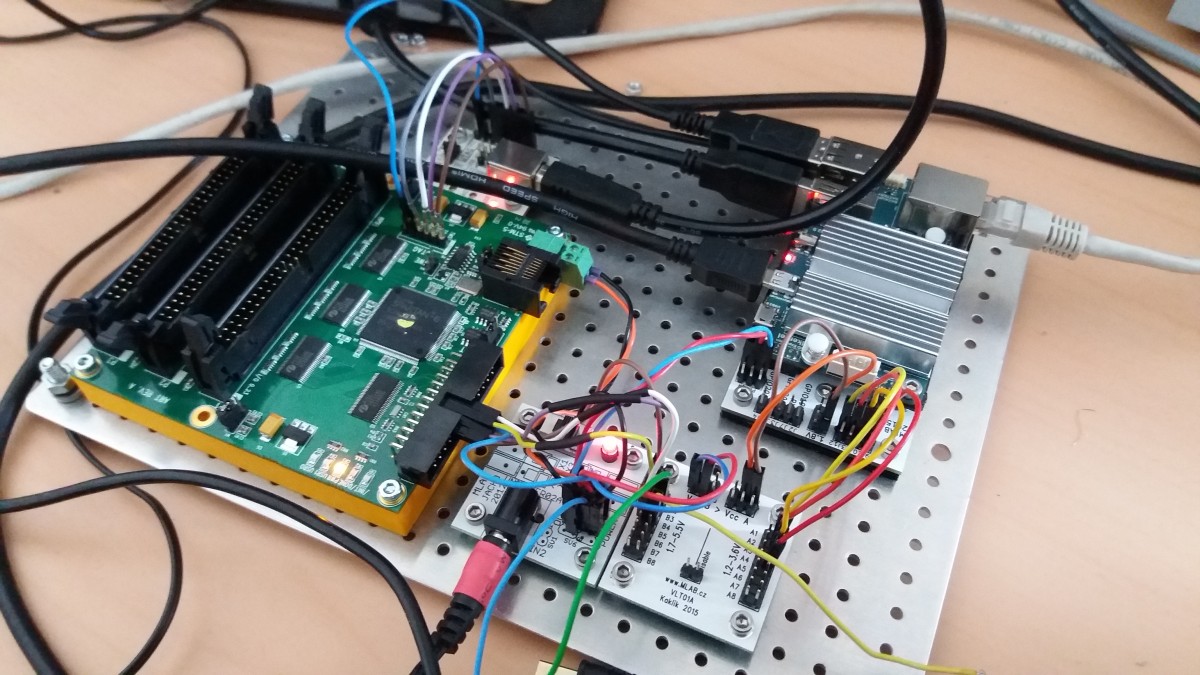

I have the first working 7i90 SPI setup. I have used the ODROID-U3 and VLT01A - MLAB voltage translator for adapt 7i90 to the ODROID's logic.

The 27 Ohm damping serial resistors are on the 7i90 translator' side covered by heat-shrink tube.

The 27 Ohm damping serial resistors are on the 7i90 translator' side covered by heat-shrink tube.

halrun

halcmd: loadrt hostmot2

Note: Using POSIX non-realtime

hm2: loading Mesa HostMot2 driver version 0.15

halcmd: loadrt hm2_spi spidev_path="/dev/spidev1.0" spidev_rate=500

probing device /dev/spidev1.0 with rate 500000 Hz

hm2/hm2_7i90.0: 72 I/O Pins used:

hm2/hm2_7i90.0: IO Pin 000 (P1-01): StepGen #0, pin Step (Output)

hm2/hm2_7i90.0: IO Pin 001 (P1-03): StepGen #0, pin Direction (Output)

hm2/hm2_7i90.0: IO Pin 002 (P1-05): StepGen #1, pin Step (Output)

hm2/hm2_7i90.0: IO Pin 003 (P1-07): StepGen #1, pin Direction (Output)

hm2/hm2_7i90.0: IO Pin 004 (P1-09): Encoder #0, pin A (Input)

hm2/hm2_7i90.0: IO Pin 005 (P1-11): Encoder #2, pin A (Input)

hm2/hm2_7i90.0: IO Pin 006 (P1-13): Encoder #0, pin B (Input)

hm2/hm2_7i90.0: IO Pin 007 (P1-15): Encoder #2, pin B (Input)

hm2/hm2_7i90.0: IO Pin 008 (P1-17): Encoder #0, pin Index (Input)

hm2/hm2_7i90.0: IO Pin 009 (P1-19): Encoder #2, pin Index (Input)

hm2/hm2_7i90.0: IO Pin 010 (P1-21): Encoder #1, pin A (Input)

hm2/hm2_7i90.0: IO Pin 011 (P1-23): Encoder #3, pin A (Input)

hm2/hm2_7i90.0: IO Pin 012 (P1-25): Encoder #1, pin B (Input)

hm2/hm2_7i90.0: IO Pin 013 (P1-27): Encoder #3, pin B (Input)

hm2/hm2_7i90.0: IO Pin 014 (P1-29): Encoder #1, pin Index (Input)

hm2/hm2_7i90.0: IO Pin 015 (P1-31): Encoder #3, pin Index (Input)

hm2/hm2_7i90.0: IO Pin 016 (P1-33): StepGen #2, pin Step (Output)

hm2/hm2_7i90.0: IO Pin 017 (P1-35): StepGen #2, pin Direction (Output)

hm2/hm2_7i90.0: IO Pin 018 (P1-37): StepGen #3, pin Step (Output)

hm2/hm2_7i90.0: IO Pin 019 (P1-39): StepGen #3, pin Direction (Output)

hm2/hm2_7i90.0: IO Pin 020 (P1-41): PWMGen #0, pin Out0 (PWM or Up) (Output)

hm2/hm2_7i90.0: IO Pin 021 (P1-43): PWMGen #0, pin Out1 (Dir or Down) (Output)

hm2/hm2_7i90.0: IO Pin 022 (P1-45): PWMGen #1, pin Out0 (PWM or Up) (Output)

hm2/hm2_7i90.0: IO Pin 023 (P1-47): PWMGen #1, pin Out1 (Dir or Down) (Output)Please Log in or Create an account to join the conversation.

- kaklik

- Offline

- New Member

-

Less

More

- Posts: 15

- Thank you received: 0

29 Mar 2016 12:42 #72319

by kaklik

Replied by kaklik on topic Mesa 7i90 in SPI mode

I have the first working 7i90 SPI setup. I have used the ODROID-U3 and VLT01A - MLAB voltage translator for adapt 7i90 to the ODROID's logic.

The 27 Ohm damping serial resistors are on the 7i90 translator' side covered by heat-shrink tube.

The 27 Ohm damping serial resistors are on the 7i90 translator' side covered by heat-shrink tube.

halrun

halcmd: loadrt hostmot2

Note: Using POSIX non-realtime

hm2: loading Mesa HostMot2 driver version 0.15

halcmd: loadrt hm2_spi spidev_path="/dev/spidev1.0" spidev_rate=500

probing device /dev/spidev1.0 with rate 500000 Hz

hm2/hm2_7i90.0: 72 I/O Pins used:

hm2/hm2_7i90.0: IO Pin 000 (P1-01): StepGen #0, pin Step (Output)

hm2/hm2_7i90.0: IO Pin 001 (P1-03): StepGen #0, pin Direction (Output)

hm2/hm2_7i90.0: IO Pin 002 (P1-05): StepGen #1, pin Step (Output)

hm2/hm2_7i90.0: IO Pin 003 (P1-07): StepGen #1, pin Direction (Output)

hm2/hm2_7i90.0: IO Pin 004 (P1-09): Encoder #0, pin A (Input)

hm2/hm2_7i90.0: IO Pin 005 (P1-11): Encoder #2, pin A (Input)

hm2/hm2_7i90.0: IO Pin 006 (P1-13): Encoder #0, pin B (Input)

hm2/hm2_7i90.0: IO Pin 007 (P1-15): Encoder #2, pin B (Input)

hm2/hm2_7i90.0: IO Pin 008 (P1-17): Encoder #0, pin Index (Input)

hm2/hm2_7i90.0: IO Pin 009 (P1-19): Encoder #2, pin Index (Input)

hm2/hm2_7i90.0: IO Pin 010 (P1-21): Encoder #1, pin A (Input)

hm2/hm2_7i90.0: IO Pin 011 (P1-23): Encoder #3, pin A (Input)

hm2/hm2_7i90.0: IO Pin 012 (P1-25): Encoder #1, pin B (Input)

hm2/hm2_7i90.0: IO Pin 013 (P1-27): Encoder #3, pin B (Input)

hm2/hm2_7i90.0: IO Pin 014 (P1-29): Encoder #1, pin Index (Input)

hm2/hm2_7i90.0: IO Pin 015 (P1-31): Encoder #3, pin Index (Input)

hm2/hm2_7i90.0: IO Pin 016 (P1-33): StepGen #2, pin Step (Output)

hm2/hm2_7i90.0: IO Pin 017 (P1-35): StepGen #2, pin Direction (Output)

hm2/hm2_7i90.0: IO Pin 018 (P1-37): StepGen #3, pin Step (Output)

hm2/hm2_7i90.0: IO Pin 019 (P1-39): StepGen #3, pin Direction (Output)

hm2/hm2_7i90.0: IO Pin 020 (P1-41): PWMGen #0, pin Out0 (PWM or Up) (Output)

hm2/hm2_7i90.0: IO Pin 021 (P1-43): PWMGen #0, pin Out1 (Dir or Down) (Output)

hm2/hm2_7i90.0: IO Pin 022 (P1-45): PWMGen #1, pin Out0 (PWM or Up) (Output)

hm2/hm2_7i90.0: IO Pin 023 (P1-47): PWMGen #1, pin Out1 (Dir or Down) (Output)Please Log in or Create an account to join the conversation.

- jepler

-

- Offline

- Administrator

-

Less

More

- Posts: 70

- Thank you received: 33

29 Mar 2016 15:55 #72340

by jepler

Replied by jepler on topic Mesa 7i90 in SPI mode

Great! As far as the C1 is concerned, if you find a solution within linuxcnc that doesn't harm functionality on the U3, please open a pull request on github.

Please Log in or Create an account to join the conversation.

- jtheath

- Offline

- New Member

-

Less

More

- Posts: 14

- Thank you received: 1

06 Oct 2016 15:39 - 06 Oct 2016 16:21 #81304

by jtheath

Replied by jtheath on topic Mesa 7i90 in SPI mode

Uncertain whether to open a new topic, different board but SPI integration challenge.

I am working on integration with RPi3. I tried the hm2_rpspi option without success. I created a new pinout for dual MX4660 configuration and first verified the new .bit file with an EPP image. Loaded the SPI image and discovered mesaflash didn't support the RPi. The challenge is the RPi spidev driver only supports 8-bit word transfers. Long story short I added code to recognize the SPI 32-bit word set failure, fallback to 8-bit transfers and do the necessary byte reordering. Good news is I have a functioning mesaflash utility (at least for readhmid).

I then ported the mesaflash logic to hm2_spi.c. Some success but consistent failure after the board is discovered. Just looking for guidance as to what I missed.

I tracked the error message down into tram.c and found the source of the trouble is the hm2->llio->send_queued_writes(hm2->llio) call from hm2_finish_write() ends up invoking hm2_spi.c::do_pending() with (nbuf == 0) so we get an immediate return 0 and the failure message.

Thank you, Joe

Here's the console output capturing stdin & stderr:

I am working on integration with RPi3. I tried the hm2_rpspi option without success. I created a new pinout for dual MX4660 configuration and first verified the new .bit file with an EPP image. Loaded the SPI image and discovered mesaflash didn't support the RPi. The challenge is the RPi spidev driver only supports 8-bit word transfers. Long story short I added code to recognize the SPI 32-bit word set failure, fallback to 8-bit transfers and do the necessary byte reordering. Good news is I have a functioning mesaflash utility (at least for readhmid).

I then ported the mesaflash logic to hm2_spi.c. Some success but consistent failure after the board is discovered. Just looking for guidance as to what I missed.

I tracked the error message down into tram.c and found the source of the trouble is the hm2->llio->send_queued_writes(hm2->llio) call from hm2_finish_write() ends up invoking hm2_spi.c::do_pending() with (nbuf == 0) so we get an immediate return 0 and the failure message.

Thank you, Joe

Here's the console output capturing stdin & stderr:

LINUXCNC - 2.8.0~pre1

Machine configuration directory is '/home/pi/linuxcnc-dev/configs/by_interface/mesa/hm2-stepper'

Machine configuration file is '7i90.ini'

Starting LinuxCNC...

Found file(REL): ./hm2-stepper.hal

Note: Using POSIX realtime

hm2: loading Mesa HostMot2 driver version 0.15

probe 24000000

fall back to 8-bit xfer

hm2/hm2_7i90.0: 72 I/O Pins used:

hm2/hm2_7i90.0: IO Pin 000 (P1-01): IOPort

hm2/hm2_7i90.0: IO Pin 001 (P1-03): StepGen #0, pin Step (Output)

hm2/hm2_7i90.0: IO Pin 002 (P1-05): StepGen #0, pin Direction (Output)

hm2/hm2_7i90.0: IO Pin 003 (P1-07): StepGen #1, pin Step (Output)

hm2/hm2_7i90.0: IO Pin 004 (P1-09): StepGen #1, pin Direction (Output)

hm2/hm2_7i90.0: IO Pin 005 (P1-11): StepGen #2, pin Step (Output)

hm2/hm2_7i90.0: IO Pin 006 (P1-13): StepGen #2, pin Direction (Output)

hm2/hm2_7i90.0: IO Pin 007 (P1-15): StepGen #3, pin Step (Output)

hm2/hm2_7i90.0: IO Pin 008 (P1-17): StepGen #3, pin Direction (Output)

hm2/hm2_7i90.0: IO Pin 009 (P1-19): IOPort

hm2/hm2_7i90.0: IO Pin 010 (P1-21): IOPort

hm2/hm2_7i90.0: IO Pin 011 (P1-23): IOPort

hm2/hm2_7i90.0: IO Pin 012 (P1-25): IOPort

hm2/hm2_7i90.0: IO Pin 013 (P1-27): PWMGen #0, pin Out0 (PWM or Up) (Output)

hm2/hm2_7i90.0: IO Pin 014 (P1-29): IOPort

hm2/hm2_7i90.0: IO Pin 015 (P1-31): StepGen #4, pin Step (Output)

hm2/hm2_7i90.0: IO Pin 016 (P1-33): IOPort

hm2/hm2_7i90.0: IO Pin 017 (P1-35): StepGen #5, pin Step (Output)

hm2/hm2_7i90.0: IO Pin 018 (P1-37): StepGen #5, pin Direction (Output)

hm2/hm2_7i90.0: IO Pin 019 (P1-39): StepGen #6, pin Step (Output)

hm2/hm2_7i90.0: IO Pin 020 (P1-41): StepGen #6, pin Direction (Output)

hm2/hm2_7i90.0: IO Pin 021 (P1-43): IOPort

hm2/hm2_7i90.0: IO Pin 022 (P1-45): IOPort

hm2/hm2_7i90.0: IO Pin 023 (P1-47): PWMGen #1, pin Out0 (PWM or Up) (Output)

hm2/hm2_7i90.0: IO Pin 024 (P2-01): IOPort

hm2/hm2_7i90.0: IO Pin 025 (P2-03): StepGen #7, pin Step (Output)

hm2/hm2_7i90.0: IO Pin 026 (P2-05): StepGen #7, pin Direction (Output)

hm2/hm2_7i90.0: IO Pin 027 (P2-07): StepGen #8, pin Step (Output)

hm2/hm2_7i90.0: IO Pin 028 (P2-09): StepGen #8, pin Direction (Output)

hm2/hm2_7i90.0: IO Pin 029 (P2-11): StepGen #9, pin Step (Output)

hm2/hm2_7i90.0: IO Pin 030 (P2-13): StepGen #9, pin Direction (Output)

hm2/hm2_7i90.0: IO Pin 031 (P2-15): StepGen #10, pin Step (Output)

hm2/hm2_7i90.0: IO Pin 032 (P2-17): StepGen #10, pin Direction (Output)

hm2/hm2_7i90.0: IO Pin 033 (P2-19): IOPort

hm2/hm2_7i90.0: IO Pin 034 (P2-21): IOPort

hm2/hm2_7i90.0: IO Pin 035 (P2-23): IOPort

hm2/hm2_7i90.0: IO Pin 036 (P2-25): IOPort

hm2/hm2_7i90.0: IO Pin 037 (P2-27): PWMGen #2, pin Out0 (PWM or Up) (Output)

hm2/hm2_7i90.0: IO Pin 038 (P2-29): IOPort

hm2/hm2_7i90.0: IO Pin 039 (P2-31): StepGen #11, pin Step (Output)

hm2/hm2_7i90.0: IO Pin 040 (P2-33): IOPort

hm2/hm2_7i90.0: IO Pin 041 (P2-35): StepGen #12, pin Step (Output)

hm2/hm2_7i90.0: IO Pin 042 (P2-37): StepGen #12, pin Direction (Output)

hm2/hm2_7i90.0: IO Pin 043 (P2-39): StepGen #13, pin Step (Output)

hm2/hm2_7i90.0: IO Pin 044 (P2-41): StepGen #13, pin Direction (Output)

hm2/hm2_7i90.0: IO Pin 045 (P2-43): IOPort

hm2/hm2_7i90.0: IO Pin 046 (P2-45): IOPort

hm2/hm2_7i90.0: IO Pin 047 (P2-47): PWMGen #3, pin Out0 (PWM or Up) (Output)

hm2/hm2_7i90.0: IO Pin 048 (P3-01): IOPort

hm2/hm2_7i90.0: IO Pin 049 (P3-03): IOPort

hm2/hm2_7i90.0: IO Pin 050 (P3-05): IOPort

hm2/hm2_7i90.0: IO Pin 051 (P3-07): IOPort

hm2/hm2_7i90.0: IO Pin 052 (P3-09): IOPort

hm2/hm2_7i90.0: IO Pin 053 (P3-11): IOPort

hm2/hm2_7i90.0: IO Pin 054 (P3-13): IOPort

hm2/hm2_7i90.0: IO Pin 055 (P3-15): IOPort

hm2/hm2_7i90.0: IO Pin 056 (P3-17): IOPort

hm2/hm2_7i90.0: IO Pin 057 (P3-19): IOPort

hm2/hm2_7i90.0: IO Pin 058 (P3-21): IOPort

hm2/hm2_7i90.0: IO Pin 059 (P3-23): IOPort

hm2/hm2_7i90.0: IO Pin 060 (P3-25): IOPort

hm2/hm2_7i90.0: IO Pin 061 (P3-27): IOPort

hm2/hm2_7i90.0: IO Pin 062 (P3-29): IOPort

hm2/hm2_7i90.0: IO Pin 063 (P3-31): IOPort

hm2/hm2_7i90.0: IO Pin 064 (P3-33): IOPort

hm2/hm2_7i90.0: IO Pin 065 (P3-35): IOPort

hm2/hm2_7i90.0: IO Pin 066 (P3-37): IOPort

hm2/hm2_7i90.0: IO Pinhm2/hm2_7i90.0: error finishing write! iter=2)

Unexpected realtime delay on task 0 with period 1000000

This Message will only display once per session.

Run the Latency Test and resolve before continuing.

Missing <max linear speed> specifier

See the 'INI Configuration' documents

Shutting down and cleaning up LinuxCNC...

task: 173 cycles, min=0.000033, max=0.030282, avg=0.008540, 0 latency excursions (> 10x expected cycle time of 0.010000s)

hm2/hm2_7i90.0: error finishing write! iter=2)

Unexpected realtime delay on task 0 with period 1000000

This Message will only display once per session.

Run the Latency Test and resolve before continuing.

067 (P3-39): IOPort

hm2/hm2_7i90.0: IO Pin 068 (P3-41): IOPort

hm2/hm2_7i90.0: IO Pin 069 (P3-43): IOPort

hm2/hm2_7i90.0: IO Pin 070 (P3-45): IOPort

hm2/hm2_7i90.0: IO Pin 071 (P3-47): IOPort

hm2/hm2_7i90.0: registered

nothing to process!!!

hm2: unloading

Note: Using POSIX realtime

Last edit: 06 Oct 2016 16:21 by andypugh. Reason: Code tags

Please Log in or Create an account to join the conversation.

- andypugh

-

- Offline

- Moderator

-

Less

More

- Posts: 19817

- Thank you received: 4616

07 Oct 2016 13:09 #81339

by andypugh

Replied by andypugh on topic Mesa 7i90 in SPI mode

It would probably be useful to have your changes incorporated into Mesaflash. But I am not sure who looks after that code. I don't _think_ is is part of LinuxCNC as such.

Please Log in or Create an account to join the conversation.

- kaklik

- Offline

- New Member

-

Less

More

- Posts: 15

- Thank you received: 0

07 Oct 2016 14:32 #81345

by kaklik

Replied by kaklik on topic Mesa 7i90 in SPI mode

I think, the only possible solution is - fix RPi3 spidev driver to support 32 bit transfers. The 32-bit word transfers are deeply integrated in linuxcnc modules. I have the same problem with ODROID-C1, which uses driver similar to RPi3 therefore it also does not support more than 8bit transfer..

Please Log in or Create an account to join the conversation.

- jepler

-

- Offline

- Administrator

-

Less

More

- Posts: 70

- Thank you received: 33

07 Oct 2016 15:06 #81348

by jepler

Replied by jepler on topic Mesa 7i90 in SPI mode

mesaflash makes its home at github.com/micges/mesaflash — I hope a pull request to make it work on a wider range of hardware would be welcomed.

My experience with /dev/spidev so far is that the drivers are typically low quality. Which is sad. Problems seem to include

This really stinks, because on the surface SPI is a perfect bus for LinuxCNC on SBCs, owing to its near-ubiquity and having a standard location on pi-like 40-pin headers to boot.

My experience with /dev/spidev so far is that the drivers are typically low quality. Which is sad. Problems seem to include

- limited transfer width support (rpi3, odroid-c1)

- incorrect byte order handling (odroid xu4, byte order is fixed in devicetree, not by ioctl)

- poor latency (u3, xu4, rpi3 without kernel patches)

This really stinks, because on the surface SPI is a perfect bus for LinuxCNC on SBCs, owing to its near-ubiquity and having a standard location on pi-like 40-pin headers to boot.

Please Log in or Create an account to join the conversation.

- tinkerer

-

- Offline

- New Member

-

Less

More

- Posts: 16

- Thank you received: 1

09 Oct 2016 22:22 - 08 Feb 2017 20:11 #81488

by tinkerer

Replied by tinkerer on topic Mesa 7i90 in SPI mode

.

Last edit: 08 Feb 2017 20:11 by tinkerer.

Please Log in or Create an account to join the conversation.

- jtheath

- Offline

- New Member

-

Less

More

- Posts: 14

- Thank you received: 1

16 Oct 2016 02:50 #81678

by jtheath

Replied by jtheath on topic Mesa 7i90 in SPI mode

Yes, I have looked at the hm2_rpspi option and not been successful (yet). Tried on two RPi3s and an RPi2 but haven't pulled it together.

I forked mesaflash and posted my 8-bit word fallback solution. Please take look at the spi_boards.c modification. I cleaned up my original work. github.com/resojoe/mesaflash

The port of this functionality to LinuxCNC itself (similar modification to src/hal/drivers/mesa-hostmot2/hm2_spi.c) seems to be working for me. If you take a close look at the RPi3 SPI driver (drivers/spi/spi-bcm2835.c) you'll find transfers handled three different ways: if a transfer is calculated to take < 30us polling logic is used; if a transfer is >96 bytes DMA is used; if neither of the first two an IRQ-based method. I don't see any sleeps or obvious slow-downs in the various paths. That said I do get an occasional "unexpected RT delay" message. Any guidance as to what to look for would be appreciated. Jepler - I did look at your SPI driver patch addressing the dynamic DMA allocation. Perhaps there is something similar in this bcm2835 module and I haven't recognized it.

Necessary config file changes:

7i90.ini - change DRIVER attribute to hm2_spi

hm2-stepper.hal - append "spi_path=/dev/spidev0.0" to the loadrt [HOSTMOT2](DRIVER) config=[HOSTMOT2](CONFIG) line.

- Joe

I forked mesaflash and posted my 8-bit word fallback solution. Please take look at the spi_boards.c modification. I cleaned up my original work. github.com/resojoe/mesaflash

The port of this functionality to LinuxCNC itself (similar modification to src/hal/drivers/mesa-hostmot2/hm2_spi.c) seems to be working for me. If you take a close look at the RPi3 SPI driver (drivers/spi/spi-bcm2835.c) you'll find transfers handled three different ways: if a transfer is calculated to take < 30us polling logic is used; if a transfer is >96 bytes DMA is used; if neither of the first two an IRQ-based method. I don't see any sleeps or obvious slow-downs in the various paths. That said I do get an occasional "unexpected RT delay" message. Any guidance as to what to look for would be appreciated. Jepler - I did look at your SPI driver patch addressing the dynamic DMA allocation. Perhaps there is something similar in this bcm2835 module and I haven't recognized it.

Necessary config file changes:

7i90.ini - change DRIVER attribute to hm2_spi

hm2-stepper.hal - append "spi_path=/dev/spidev0.0" to the loadrt [HOSTMOT2](DRIVER) config=[HOSTMOT2](CONFIG) line.

- Joe

Please Log in or Create an account to join the conversation.

- jepler

-

- Offline

- Administrator

-

Less

More

- Posts: 70

- Thank you received: 33

16 Oct 2016 21:16 #81701

by jepler

Replied by jepler on topic Mesa 7i90 in SPI mode

The changes on github look good to me in general. My ARM hardware is all put away so I can't test it right now, though.

I did go ahead and create a pull request on github, so that hopefully micges will incorporate your change.

Thanks!

I did go ahead and create a pull request on github, so that hopefully micges will incorporate your change.

Thanks!

Please Log in or Create an account to join the conversation.

Moderators: PCW, jmelson

Time to create page: 0.145 seconds