Mesa 7i96+7i85+7i84

- ikkuh

-

Topic Author

Topic Author

- Offline

- Elite Member

-

Less

More

- Posts: 273

- Thank you received: 48

29 Dec 2021 09:36 #230206

by ikkuh

Mesa 7i96+7i85+7i84 was created by ikkuh

Hi,

Hopefuly PCM can help me with this.

I have a 7i96 card, flashed with standard firmware. I also have a 7i85 connected to p3. This all works great.

Now I have bought a 7i84 and wonder if I have to adjust anything on the 7i96 to get it working? Or will it work straight out of the box?

Don't have the card yet, should arrive this afternoon.

Hopefuly PCM can help me with this.

I have a 7i96 card, flashed with standard firmware. I also have a 7i85 connected to p3. This all works great.

Now I have bought a 7i84 and wonder if I have to adjust anything on the 7i96 to get it working? Or will it work straight out of the box?

Don't have the card yet, should arrive this afternoon.

Please Log in or Create an account to join the conversation.

- tommylight

-

- Offline

- Moderator

-

Less

More

- Posts: 21467

- Thank you received: 7320

29 Dec 2021 12:44 #230223

by tommylight

Replied by tommylight on topic Mesa 7i96+7i85+7i84

7i84 is an I/O port with 32 in and 16 out, right ?

It connects to FPGA via smart serial, so if you have a free sserial on the 7i96 ( i do not know if 7i96 has it, still waiting for mine), use a RJ45 connector or an ethernet cable cut in half.

It does not require any programming flashing of cards.

It connects to FPGA via smart serial, so if you have a free sserial on the 7i96 ( i do not know if 7i96 has it, still waiting for mine), use a RJ45 connector or an ethernet cable cut in half.

It does not require any programming flashing of cards.

The following user(s) said Thank You: ikkuh

Please Log in or Create an account to join the conversation.

- ikkuh

-

Topic Author

Topic Author

- Offline

- Elite Member

-

Less

More

- Posts: 273

- Thank you received: 48

29 Dec 2021 12:54 #230225

by ikkuh

Replied by ikkuh on topic Mesa 7i96+7i85+7i84

Thanks, card just arrived and is connected. Does not work yet, but I will struggle on.7i84 is an I/O port with 32 in and 16 out, right ?

It connects to FPGA via smart serial, so if you have a free sserial on the 7i96 ( i do not know if 7i96 has it, still waiting for mine), use a RJ45 connector or an ethernet cable cut in half.

It does not require any programming flashing of cards.

Please Log in or Create an account to join the conversation.

- tommylight

-

- Offline

- Moderator

-

Less

More

- Posts: 21467

- Thank you received: 7320

29 Dec 2021 13:03 #230227

by tommylight

Replied by tommylight on topic Mesa 7i96+7i85+7i84

Did you power it with field power?

Also check the manual for cabling, it has a simple solution for the ethernet cable.

Start LinuxCNC, got to machine menu and open "show hal configuration", there on the left side navigate to find the 7i84.

Also check the manual for cabling, it has a simple solution for the ethernet cable.

Start LinuxCNC, got to machine menu and open "show hal configuration", there on the left side navigate to find the 7i84.

The following user(s) said Thank You: ikkuh

Please Log in or Create an account to join the conversation.

- ikkuh

-

Topic Author

Topic Author

- Offline

- Elite Member

-

Less

More

- Posts: 273

- Thank you received: 48

29 Dec 2021 13:18 - 29 Dec 2021 13:19 #230229

by ikkuh

Replied by ikkuh on topic Mesa 7i96+7i85+7i84

CAN SOMEONE FIX THIS BLOODY AWFUL EDITOR????????????????????????????

Yes, everything is connected. Field voltage 12v, logic 12vBut it looks like my 7i96 does not have the correct sserial connections.Configuration Name: HOSTMOT2General configuration information: BoardName : MESA7I96 FPGA Size: 9 KGates FPGA Pins: 144 Number of IO Ports: 3 Width of one I/O port: 17 Clock Low frequency: 100.0000 MHz Clock High frequency: 200.0000 MHz IDROM Type: 3 Instance Stride 0: 4 Instance Stride 1: 64 Register Stride 0: 256 Register Stride 1: 256Modules in configuration: Module: DPLL There are 1 of DPLL in configuration Version: 0 Registers: 7 BaseAddress: 7000 ClockFrequency: 100.000 MHz Register Stride: 256 bytes Instance Stride: 4 bytes Module: WatchDog There are 1 of WatchDog in configuration Version: 0 Registers: 3 BaseAddress: 0C00 ClockFrequency: 100.000 MHz Register Stride: 256 bytes Instance Stride: 4 bytes Module: IOPort There are 3 of IOPort in configuration Version: 0 Registers: 5 BaseAddress: 1000 ClockFrequency: 100.000 MHz Register Stride: 256 bytes Instance Stride: 4 bytes Module: PWM There are 1 of PWM in configuration Version: 0 Registers: 5 BaseAddress: 4100 ClockFrequency: 200.000 MHz Register Stride: 256 bytes Instance Stride: 4 bytes Module: StepGen There are 4 of StepGen in configuration Version: 2 Registers: 10 BaseAddress: 2000 ClockFrequency: 100.000 MHz Register Stride: 256 bytes Instance Stride: 4 bytes Module: QCount There are 1 of QCount in configuration Version: 2 Registers: 5 BaseAddress: 3000 ClockFrequency: 100.000 MHz Register Stride: 256 bytes Instance Stride: 4 bytes Module: SSerial There are 1 of SSerial in configuration Version: 0 Registers: 6 BaseAddress: 5B00 ClockFrequency: 100.000 MHz Register Stride: 256 bytes Instance Stride: 64 bytes Module: SSR There are 1 of SSR in configuration Version: 0 Registers: 2 BaseAddress: 7D00 ClockFrequency: 100.000 MHz Register Stride: 256 bytes Instance Stride: 4 bytes Module: LED There are 1 of LED in configuration Version: 0 Registers: 1 BaseAddress: 0200 ClockFrequency: 100.000 MHz Register Stride: 256 bytes Instance Stride: 4 bytesConfiguration pin-out:IO Connections for TB3Pin

Yes, everything is connected. Field voltage 12v, logic 12vBut it looks like my 7i96 does not have the correct sserial connections.Configuration Name: HOSTMOT2General configuration information: BoardName : MESA7I96 FPGA Size: 9 KGates FPGA Pins: 144 Number of IO Ports: 3 Width of one I/O port: 17 Clock Low frequency: 100.0000 MHz Clock High frequency: 200.0000 MHz IDROM Type: 3 Instance Stride 0: 4 Instance Stride 1: 64 Register Stride 0: 256 Register Stride 1: 256Modules in configuration: Module: DPLL There are 1 of DPLL in configuration Version: 0 Registers: 7 BaseAddress: 7000 ClockFrequency: 100.000 MHz Register Stride: 256 bytes Instance Stride: 4 bytes Module: WatchDog There are 1 of WatchDog in configuration Version: 0 Registers: 3 BaseAddress: 0C00 ClockFrequency: 100.000 MHz Register Stride: 256 bytes Instance Stride: 4 bytes Module: IOPort There are 3 of IOPort in configuration Version: 0 Registers: 5 BaseAddress: 1000 ClockFrequency: 100.000 MHz Register Stride: 256 bytes Instance Stride: 4 bytes Module: PWM There are 1 of PWM in configuration Version: 0 Registers: 5 BaseAddress: 4100 ClockFrequency: 200.000 MHz Register Stride: 256 bytes Instance Stride: 4 bytes Module: StepGen There are 4 of StepGen in configuration Version: 2 Registers: 10 BaseAddress: 2000 ClockFrequency: 100.000 MHz Register Stride: 256 bytes Instance Stride: 4 bytes Module: QCount There are 1 of QCount in configuration Version: 2 Registers: 5 BaseAddress: 3000 ClockFrequency: 100.000 MHz Register Stride: 256 bytes Instance Stride: 4 bytes Module: SSerial There are 1 of SSerial in configuration Version: 0 Registers: 6 BaseAddress: 5B00 ClockFrequency: 100.000 MHz Register Stride: 256 bytes Instance Stride: 64 bytes Module: SSR There are 1 of SSR in configuration Version: 0 Registers: 2 BaseAddress: 7D00 ClockFrequency: 100.000 MHz Register Stride: 256 bytes Instance Stride: 4 bytes Module: LED There are 1 of LED in configuration Version: 0 Registers: 1 BaseAddress: 0200 ClockFrequency: 100.000 MHz Register Stride: 256 bytes Instance Stride: 4 bytesConfiguration pin-out:IO Connections for TB3Pin

Last edit: 29 Dec 2021 13:19 by ikkuh.

Please Log in or Create an account to join the conversation.

- ikkuh

-

Topic Author

Topic Author

- Offline

- Elite Member

-

Less

More

- Posts: 273

- Thank you received: 48

29 Dec 2021 13:20 #230230

by ikkuh

Replied by ikkuh on topic Mesa 7i96+7i85+7i84

Configuration Name: HOSTMOT2

General configuration information:

BoardName : MESA7I96

FPGA Size: 9 KGates

FPGA Pins: 144

Number of IO Ports: 3

Width of one I/O port: 17

Clock Low frequency: 100.0000 MHz

Clock High frequency: 200.0000 MHz

IDROM Type: 3

Instance Stride 0: 4

Instance Stride 1: 64

Register Stride 0: 256

Register Stride 1: 256

Modules in configuration:

Module: DPLL

There are 1 of DPLL in configuration

Version: 0

Registers: 7

BaseAddress: 7000

ClockFrequency: 100.000 MHz

Register Stride: 256 bytes

Instance Stride: 4 bytes

Module: WatchDog

There are 1 of WatchDog in configuration

Version: 0

Registers: 3

BaseAddress: 0C00

ClockFrequency: 100.000 MHz

Register Stride: 256 bytes

Instance Stride: 4 bytes

Module: IOPort

There are 3 of IOPort in configuration

Version: 0

Registers: 5

BaseAddress: 1000

ClockFrequency: 100.000 MHz

Register Stride: 256 bytes

Instance Stride: 4 bytes

Module: PWM

There are 1 of PWM in configuration

Version: 0

Registers: 5

BaseAddress: 4100

ClockFrequency: 200.000 MHz

Register Stride: 256 bytes

Instance Stride: 4 bytes

Module: StepGen

There are 10 of StepGen in configuration

Version: 2

Registers: 10

BaseAddress: 2000

ClockFrequency: 100.000 MHz

Register Stride: 256 bytes

Instance Stride: 4 bytes

Module: QCount

There are 2 of QCount in configuration

Version: 2

Registers: 5

BaseAddress: 3000

ClockFrequency: 100.000 MHz

Register Stride: 256 bytes

Instance Stride: 4 bytes

Module: SSerial

There are 1 of SSerial in configuration

Version: 0

Registers: 6

BaseAddress: 5B00

ClockFrequency: 100.000 MHz

Register Stride: 256 bytes

Instance Stride: 64 bytes

Module: SSR

There are 1 of SSR in configuration

Version: 0

Registers: 2

BaseAddress: 7D00

ClockFrequency: 100.000 MHz

Register Stride: 256 bytes

Instance Stride: 4 bytes

Module: LED

There are 1 of LED in configuration

Version: 0

Registers: 1

BaseAddress: 0200

ClockFrequency: 100.000 MHz

Register Stride: 256 bytes

Instance Stride: 4 bytes

Configuration pin-out:

IO Connections for TB3

Pin# I/O Pri. func Sec. func Chan Pin func Pin Dir

1 0 IOPort None

14 1 IOPort None

2 2 IOPort None

15 3 IOPort None

3 4 IOPort None

16 5 IOPort None

4 6 IOPort None

17 7 IOPort None

5 8 IOPort None

6 9 IOPort None

7 10 IOPort None

8 11 IOPort SSR 0 Out-00 (Out)

9 12 IOPort SSR 0 Out-01 (Out)

10 13 IOPort SSR 0 Out-02 (Out)

11 14 IOPort SSR 0 Out-03 (Out)

12 15 IOPort SSR 0 Out-04 (Out)

13 16 IOPort SSR 0 Out-05 (Out)

IO Connections for TB1/TB2

Pin# I/O Pri. func Sec. func Chan Pin func Pin Dir

1 17 IOPort StepGen 0 Step/Table1 (Out)

14 18 IOPort StepGen 0 Dir/Table2 (Out)

2 19 IOPort StepGen 1 Step/Table1 (Out)

15 20 IOPort StepGen 1 Dir/Table2 (Out)

3 21 IOPort StepGen 2 Step/Table1 (Out)

16 22 IOPort StepGen 2 Dir/Table2 (Out)

4 23 IOPort StepGen 3 Step/Table1 (Out)

17 24 IOPort StepGen 3 Dir/Table2 (Out)

5 25 IOPort StepGen 4 Step/Table1 (Out)

6 26 IOPort StepGen 4 Dir/Table2 (Out)

7 27 IOPort QCount 0 Quad-A (In)

8 28 IOPort QCount 0 Quad-B (In)

9 29 IOPort QCount 0 Quad-IDX (In)

10 30 IOPort SSerial 0 RXData0 (In)

11 31 IOPort SSerial 0 TXData0 (Out)

12 32 IOPort SSerial 0 TXEn0 (Out)

13 33 IOPort SSR 0 AC Ref (Out)

IO Connections for P1

Pin# I/O Pri. func Sec. func Chan Pin func Pin Dir

1 34 IOPort StepGen 5 Dir/Table2 (Out)

14 35 IOPort StepGen 5 Step/Table1 (Out)

2 36 IOPort StepGen 6 Dir/Table2 (Out)

15 37 IOPort StepGen 6 Step/Table1 (Out)

3 38 IOPort StepGen 7 Dir/Table2 (Out)

16 39 IOPort StepGen 7 Step/Table1 (Out)

4 40 IOPort StepGen 8 Dir/Table2 (Out)

17 41 IOPort StepGen 8 Step/Table1 (Out)

5 42 IOPort StepGen 9 Dir/Table2 (Out)

6 43 IOPort StepGen 9 Step/Table1 (Out)

7 44 IOPort SSerial 0 TXData1 (Out)

8 45 IOPort SSerial 0 RXData1 (In)

9 46 IOPort SSerial 0 TXData2 (Out)

10 47 IOPort SSerial 0 RXData2 (In)

11 48 IOPort QCount 1 Quad-IDX (In)

12 49 IOPort QCount 1 Quad-B (In)

13 50 IOPort QCount 1 Quad-A (In)

General configuration information:

BoardName : MESA7I96

FPGA Size: 9 KGates

FPGA Pins: 144

Number of IO Ports: 3

Width of one I/O port: 17

Clock Low frequency: 100.0000 MHz

Clock High frequency: 200.0000 MHz

IDROM Type: 3

Instance Stride 0: 4

Instance Stride 1: 64

Register Stride 0: 256

Register Stride 1: 256

Modules in configuration:

Module: DPLL

There are 1 of DPLL in configuration

Version: 0

Registers: 7

BaseAddress: 7000

ClockFrequency: 100.000 MHz

Register Stride: 256 bytes

Instance Stride: 4 bytes

Module: WatchDog

There are 1 of WatchDog in configuration

Version: 0

Registers: 3

BaseAddress: 0C00

ClockFrequency: 100.000 MHz

Register Stride: 256 bytes

Instance Stride: 4 bytes

Module: IOPort

There are 3 of IOPort in configuration

Version: 0

Registers: 5

BaseAddress: 1000

ClockFrequency: 100.000 MHz

Register Stride: 256 bytes

Instance Stride: 4 bytes

Module: PWM

There are 1 of PWM in configuration

Version: 0

Registers: 5

BaseAddress: 4100

ClockFrequency: 200.000 MHz

Register Stride: 256 bytes

Instance Stride: 4 bytes

Module: StepGen

There are 10 of StepGen in configuration

Version: 2

Registers: 10

BaseAddress: 2000

ClockFrequency: 100.000 MHz

Register Stride: 256 bytes

Instance Stride: 4 bytes

Module: QCount

There are 2 of QCount in configuration

Version: 2

Registers: 5

BaseAddress: 3000

ClockFrequency: 100.000 MHz

Register Stride: 256 bytes

Instance Stride: 4 bytes

Module: SSerial

There are 1 of SSerial in configuration

Version: 0

Registers: 6

BaseAddress: 5B00

ClockFrequency: 100.000 MHz

Register Stride: 256 bytes

Instance Stride: 64 bytes

Module: SSR

There are 1 of SSR in configuration

Version: 0

Registers: 2

BaseAddress: 7D00

ClockFrequency: 100.000 MHz

Register Stride: 256 bytes

Instance Stride: 4 bytes

Module: LED

There are 1 of LED in configuration

Version: 0

Registers: 1

BaseAddress: 0200

ClockFrequency: 100.000 MHz

Register Stride: 256 bytes

Instance Stride: 4 bytes

Configuration pin-out:

IO Connections for TB3

Pin# I/O Pri. func Sec. func Chan Pin func Pin Dir

1 0 IOPort None

14 1 IOPort None

2 2 IOPort None

15 3 IOPort None

3 4 IOPort None

16 5 IOPort None

4 6 IOPort None

17 7 IOPort None

5 8 IOPort None

6 9 IOPort None

7 10 IOPort None

8 11 IOPort SSR 0 Out-00 (Out)

9 12 IOPort SSR 0 Out-01 (Out)

10 13 IOPort SSR 0 Out-02 (Out)

11 14 IOPort SSR 0 Out-03 (Out)

12 15 IOPort SSR 0 Out-04 (Out)

13 16 IOPort SSR 0 Out-05 (Out)

IO Connections for TB1/TB2

Pin# I/O Pri. func Sec. func Chan Pin func Pin Dir

1 17 IOPort StepGen 0 Step/Table1 (Out)

14 18 IOPort StepGen 0 Dir/Table2 (Out)

2 19 IOPort StepGen 1 Step/Table1 (Out)

15 20 IOPort StepGen 1 Dir/Table2 (Out)

3 21 IOPort StepGen 2 Step/Table1 (Out)

16 22 IOPort StepGen 2 Dir/Table2 (Out)

4 23 IOPort StepGen 3 Step/Table1 (Out)

17 24 IOPort StepGen 3 Dir/Table2 (Out)

5 25 IOPort StepGen 4 Step/Table1 (Out)

6 26 IOPort StepGen 4 Dir/Table2 (Out)

7 27 IOPort QCount 0 Quad-A (In)

8 28 IOPort QCount 0 Quad-B (In)

9 29 IOPort QCount 0 Quad-IDX (In)

10 30 IOPort SSerial 0 RXData0 (In)

11 31 IOPort SSerial 0 TXData0 (Out)

12 32 IOPort SSerial 0 TXEn0 (Out)

13 33 IOPort SSR 0 AC Ref (Out)

IO Connections for P1

Pin# I/O Pri. func Sec. func Chan Pin func Pin Dir

1 34 IOPort StepGen 5 Dir/Table2 (Out)

14 35 IOPort StepGen 5 Step/Table1 (Out)

2 36 IOPort StepGen 6 Dir/Table2 (Out)

15 37 IOPort StepGen 6 Step/Table1 (Out)

3 38 IOPort StepGen 7 Dir/Table2 (Out)

16 39 IOPort StepGen 7 Step/Table1 (Out)

4 40 IOPort StepGen 8 Dir/Table2 (Out)

17 41 IOPort StepGen 8 Step/Table1 (Out)

5 42 IOPort StepGen 9 Dir/Table2 (Out)

6 43 IOPort StepGen 9 Step/Table1 (Out)

7 44 IOPort SSerial 0 TXData1 (Out)

8 45 IOPort SSerial 0 RXData1 (In)

9 46 IOPort SSerial 0 TXData2 (Out)

10 47 IOPort SSerial 0 RXData2 (In)

11 48 IOPort QCount 1 Quad-IDX (In)

12 49 IOPort QCount 1 Quad-B (In)

13 50 IOPort QCount 1 Quad-A (In)

Please Log in or Create an account to join the conversation.

- ikkuh

-

Topic Author

Topic Author

- Offline

- Elite Member

-

Less

More

- Posts: 273

- Thank you received: 48

29 Dec 2021 13:21 #230231

by ikkuh

Replied by ikkuh on topic Mesa 7i96+7i85+7i84

I give up, this editor is more annoying then fixing the problem itself. Takes even more time.

Please Log in or Create an account to join the conversation.

- PCW

-

- Away

- Moderator

-

Less

More

- Posts: 17828

- Thank you received: 5218

29 Dec 2021 16:15 - 29 Dec 2021 16:16 #230248

by PCW

Replied by PCW on topic Mesa 7i96+7i85+7i84

To get the 7I84 working you should have the jumpers in the default position

(W1 and W2 in the left position), field power applied to both A and B sides,

and the correct RJ45 cable.

When LinuxCNC is not running but everything is powered up, you should have

two yellow and one red LED illuminated. When LinuxCNC is running, the red

LED should extinguish and you should get a blinking green LED instead.

(W1 and W2 in the left position), field power applied to both A and B sides,

and the correct RJ45 cable.

When LinuxCNC is not running but everything is powered up, you should have

two yellow and one red LED illuminated. When LinuxCNC is running, the red

LED should extinguish and you should get a blinking green LED instead.

Last edit: 29 Dec 2021 16:16 by PCW.

The following user(s) said Thank You: tommylight

Please Log in or Create an account to join the conversation.

- ikkuh

-

Topic Author

Topic Author

- Offline

- Elite Member

-

Less

More

- Posts: 273

- Thank you received: 48

29 Dec 2021 17:09 #230255

by ikkuh

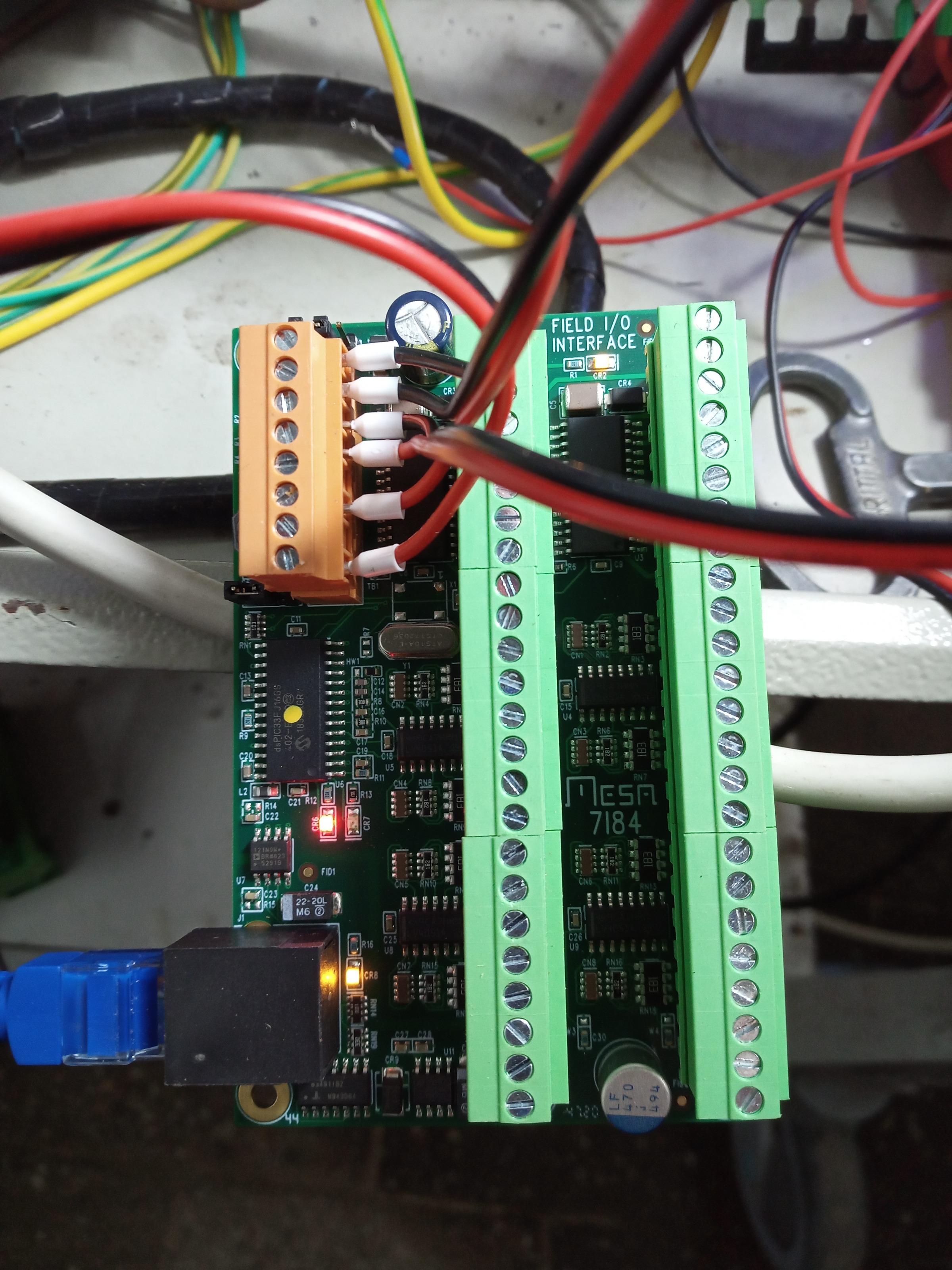

Here are pictures of the leds and jumpers LinuxCNC not running

Replied by ikkuh on topic Mesa 7i96+7i85+7i84

Thanks!To get the 7I84 working you should have the jumpers in the default position

(W1 and W2 in the left position), field power applied to both A and B sides,

and the correct RJ45 cable.

When LinuxCNC is not running but everything is powered up, you should have

two yellow and one red LED illuminated. When LinuxCNC is running, the red

LED should extinguish and you should get a blinking green LED instead.

Here are pictures of the leds and jumpers LinuxCNC not running

Attachments:

Please Log in or Create an account to join the conversation.

- PCW

-

- Away

- Moderator

-

Less

More

- Posts: 17828

- Thank you received: 5218

29 Dec 2021 17:15 #230257

by PCW

Replied by PCW on topic Mesa 7i96+7i85+7i84

Possibly a cable error of some kind

Please Log in or Create an account to join the conversation.

Moderators: PCW, jmelson

Time to create page: 0.191 seconds