Search Results (Searched for: )

- Thayloreing

- Thayloreing

16 Dec 2024 14:30

Replied by Thayloreing on topic Position Logger

Position Logger

Category: General LinuxCNC Questions

- spicer

16 Dec 2024 14:13

Replied by spicer on topic Linux CNC auf Virtualbox Simulation

Linux CNC auf Virtualbox Simulation

Category: Deutsch

- onceloved

16 Dec 2024 13:54

Replied by onceloved on topic Home position using ethercat servo position (absolute encoder value).

Home position using ethercat servo position (absolute encoder value).

Category: General LinuxCNC Questions

- spumco

- spumco

16 Dec 2024 13:53 - 16 Dec 2024 13:54

Replied by spumco on topic Rotary Selector Switches & Resistors

Rotary Selector Switches & Resistors

Category: General LinuxCNC Questions

- Ricoch3T

- Ricoch3T

16 Dec 2024 13:52

- kjlty

- kjlty

16 Dec 2024 13:37

- horcsab

- horcsab

16 Dec 2024 13:34

- meister

- meister

16 Dec 2024 13:24

Replied by meister on topic LinuxCNC-RIO - RealtimeIO for LinuxCNC based on FPGA (ICE40 / ECP5)

LinuxCNC-RIO - RealtimeIO for LinuxCNC based on FPGA (ICE40 / ECP5)

Category: Computers and Hardware

- kjlty

- kjlty

16 Dec 2024 13:16

- PatJac

- PatJac

16 Dec 2024 13:07

Replied by PatJac on topic Real-Time Kernel with Orange Pi 4 LTS

Real-Time Kernel with Orange Pi 4 LTS

Category: General LinuxCNC Questions

- MirkoCNC

- MirkoCNC

16 Dec 2024 13:02 - 16 Dec 2024 13:02

Replied by MirkoCNC on topic LinuxCNC-RIO - RealtimeIO for LinuxCNC based on FPGA (ICE40 / ECP5)

LinuxCNC-RIO - RealtimeIO for LinuxCNC based on FPGA (ICE40 / ECP5)

Category: Computers and Hardware

- csurimilan

- csurimilan

16 Dec 2024 12:51

- ABurkD

- ABurkD

16 Dec 2024 12:26

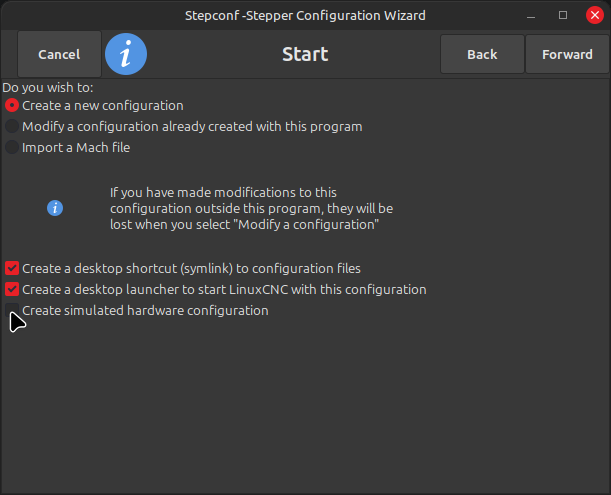

Replied by ABurkD on topic Stefconf: Wizard stellt immer auf Simulator, wie änder ich das?

Stefconf: Wizard stellt immer auf Simulator, wie änder ich das?

Category: Deutsch

- tommylight

16 Dec 2024 12:18

Replied by tommylight on topic Stefconf: Wizard stellt immer auf Simulator, wie änder ich das?

Stefconf: Wizard stellt immer auf Simulator, wie änder ich das?

Category: Deutsch

Time to create page: 0.397 seconds