- Hardware & Machines

- Computers and Hardware

- LinuxCNC-RIO - RealtimeIO for LinuxCNC based on FPGA (ICE40 / ECP5)

LinuxCNC-RIO - RealtimeIO for LinuxCNC based on FPGA (ICE40 / ECP5)

- meister

- Offline

- Platinum Member

-

Less

More

- Posts: 730

- Thank you received: 445

05 Aug 2024 11:49 #306990

by meister

Replied by meister on topic LinuxCNC-RIO - RealtimeIO for LinuxCNC based on FPGA (ICE40 / ECP5)

@all

how do you implement differential signals?

i wanted to try it now with the AM26LS32, there are also some from MAX but they are extremely expensive

how do you implement differential signals?

i wanted to try it now with the AM26LS32, there are also some from MAX but they are extremely expensive

Please Log in or Create an account to join the conversation.

- PCW

-

- Offline

- Moderator

-

Less

More

- Posts: 17864

- Thank you received: 5231

05 Aug 2024 14:28 #307001

by PCW

Replied by PCW on topic LinuxCNC-RIO - RealtimeIO for LinuxCNC based on FPGA (ICE40 / ECP5)

We use 26LS32's a lot for a couple of reasons:

1. Their inputs are protected from up to +-25V

(the more expensive CMOS parts are typically protected to only +-14V or so)

2. Because they are TTL parts the outputs don't swing to 5V and if you add a 1K

pulldown, the outputs are OK for interfacing with most 3.3V chips.

3. They are much cheaper than the CMOS equivalents.

The main disadvantage is higher power consumption

1. Their inputs are protected from up to +-25V

(the more expensive CMOS parts are typically protected to only +-14V or so)

2. Because they are TTL parts the outputs don't swing to 5V and if you add a 1K

pulldown, the outputs are OK for interfacing with most 3.3V chips.

3. They are much cheaper than the CMOS equivalents.

The main disadvantage is higher power consumption

The following user(s) said Thank You: tommylight, meister, Mecanix

Please Log in or Create an account to join the conversation.

- meister

- Offline

- Platinum Member

-

Less

More

- Posts: 730

- Thank you received: 445

05 Aug 2024 16:09 #307008

by meister

Replied by meister on topic LinuxCNC-RIO - RealtimeIO for LinuxCNC based on FPGA (ICE40 / ECP5)

thank you PCW !

the Linear Scale works with quadencoder(z) plugin

but the part from my link is really cheap,

ok for playing around, but to use it properly, hmm, no

the Linear Scale works with quadencoder(z) plugin

but the part from my link is really cheap,

ok for playing around, but to use it properly, hmm, no

Please Log in or Create an account to join the conversation.

- Mecanix

- Offline

- Platinum Member

-

Less

More

- Posts: 447

- Thank you received: 227

05 Aug 2024 16:36 #307010

by Mecanix

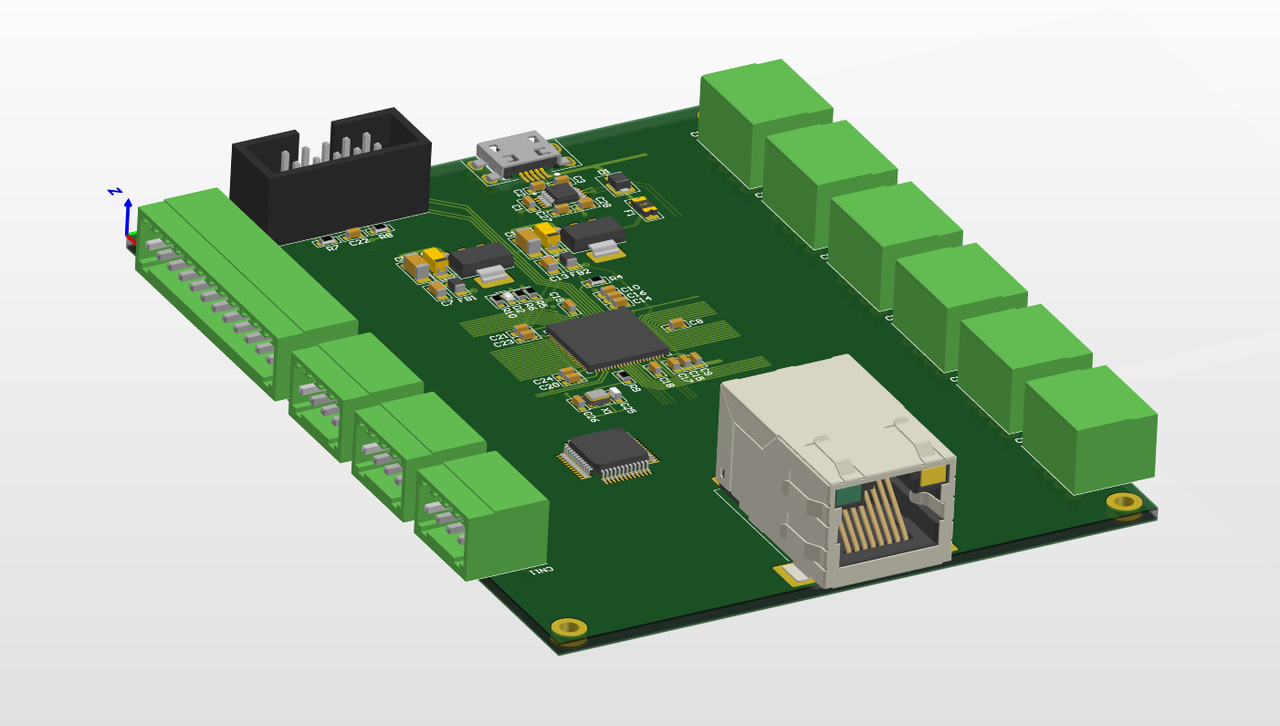

In the other RIO gossips; a brand new journey is about to begin!! However and before I begin routing this I wanted to poke your expertise and ask what would define a half-perfect RIO Motion Control Board. Is there anything fancy that we need on that other than the usual SPINDLE + MPG + XYZAB + Ins & Outs?

Replied by Mecanix on topic LinuxCNC-RIO - RealtimeIO for LinuxCNC based on FPGA (ICE40 / ECP5)

Haha that's so cool. Their output are indeed identical to those 90deg ABZ rotary encoder. Plugs right in your quadencoderz plugin and so no extra work required!new toy

works like a rotary-encoder, i think it should work in RIO

In the other RIO gossips; a brand new journey is about to begin!! However and before I begin routing this I wanted to poke your expertise and ask what would define a half-perfect RIO Motion Control Board. Is there anything fancy that we need on that other than the usual SPINDLE + MPG + XYZAB + Ins & Outs?

Please Log in or Create an account to join the conversation.

- meister

- Offline

- Platinum Member

-

Less

More

- Posts: 730

- Thank you received: 445

05 Aug 2024 21:35 #307034

by meister

Replied by meister on topic LinuxCNC-RIO - RealtimeIO for LinuxCNC based on FPGA (ICE40 / ECP5)

Sorry, was busy

@Mecanix

nice board !, but i answer you tomorrow, need sleep now

@Mecanix

nice board !, but i answer you tomorrow, need sleep now

The following user(s) said Thank You: Mecanix

Please Log in or Create an account to join the conversation.

- meister

- Offline

- Platinum Member

-

Less

More

- Posts: 730

- Thank you received: 445

06 Aug 2024 05:39 - 06 Aug 2024 06:29 #307058

by meister

Replied by meister on topic LinuxCNC-RIO - RealtimeIO for LinuxCNC based on FPGA (ICE40 / ECP5)

>In the other RIO gossips; a brand new journey is about to begin!! However and before I

>begin routing this I wanted to poke your expertise and ask what would define a half-

>perfect RIO Motion Control Board. Is there anything fancy that we need on that other

>than the usual SPINDLE + MPG + XYZAB + Ins & Outs?

it always depends on the application,

as a universal board, I would say:

4 step/dir

4 inputs (selectable 24V/5V - Proximity Limit Switch)

1 encoder (for lathe / with differantal inputs)

>=3 inputs (for estop/misc)

>=3 outputs (cooling/spindle)

1 MODUS (vfd-spindle)

1 WS2812b (status display / only one pin needed)

1 PMOD header

I really like these connectors: www.reichelt.de/stiftleiste-2-pol-rm-3-5...rank&OFFSET=16&nbc=1

but it's a matter of taste

i think USB/Seriel is not necessary

the fpga on the tangnano20k has the same housing, if the pinout matches you could also use it !?!?!

not the same

EDIT: and it should work with cheap programmer like the USB-Blaster

>begin routing this I wanted to poke your expertise and ask what would define a half-

>perfect RIO Motion Control Board. Is there anything fancy that we need on that other

>than the usual SPINDLE + MPG + XYZAB + Ins & Outs?

it always depends on the application,

as a universal board, I would say:

4 step/dir

4 inputs (selectable 24V/5V - Proximity Limit Switch)

1 encoder (for lathe / with differantal inputs)

>=3 inputs (for estop/misc)

>=3 outputs (cooling/spindle)

1 MODUS (vfd-spindle)

1 WS2812b (status display / only one pin needed)

1 PMOD header

I really like these connectors: www.reichelt.de/stiftleiste-2-pol-rm-3-5...rank&OFFSET=16&nbc=1

but it's a matter of taste

i think USB/Seriel is not necessary

not the same

EDIT: and it should work with cheap programmer like the USB-Blaster

Last edit: 06 Aug 2024 06:29 by meister.

The following user(s) said Thank You: Mecanix

Please Log in or Create an account to join the conversation.

- meister

- Offline

- Platinum Member

-

Less

More

- Posts: 730

- Thank you received: 445

06 Aug 2024 07:32 - 06 Aug 2024 07:36 #307059

by meister

Replied by meister on topic LinuxCNC-RIO - RealtimeIO for LinuxCNC based on FPGA (ICE40 / ECP5)

i have noticed that you can also generate verilog with litex without soft-core. and that liteeth also supports UDP in hardware. I think it should be possible to build a UDP interface that runs on the Colorlite boards (and others) and can be integrated into RIO.

There are many supported FPGA's and PHY's: github.com/enjoy-digital/liteeth

There are many supported FPGA's and PHY's: github.com/enjoy-digital/liteeth

Last edit: 06 Aug 2024 07:36 by meister.

Please Log in or Create an account to join the conversation.

- kzali

- Offline

- Junior Member

-

Less

More

- Posts: 35

- Thank you received: 12

06 Aug 2024 07:59 #307060

by kzali

Replied by kzali on topic LinuxCNC-RIO - RealtimeIO for LinuxCNC based on FPGA (ICE40 / ECP5)

Would the Tang Primer 20k be a good candidatei have noticed that you can also generate verilog with litex without soft-core. and that liteeth also supports UDP in hardware. I think it should be possible to build a UDP interface that runs on the Colorlite boards (and others) and can be integrated into RIO.

There are many supported FPGA's and PHY's: github.com/enjoy-digital/liteeth

Please Log in or Create an account to join the conversation.

- meister

- Offline

- Platinum Member

-

Less

More

- Posts: 730

- Thank you received: 445

06 Aug 2024 08:04 #307061

by meister

Replied by meister on topic LinuxCNC-RIO - RealtimeIO for LinuxCNC based on FPGA (ICE40 / ECP5)

unfortunately i don't know much about litex and i don't know if it is supported.

but for the tangprimer20k on the dock ext-board there is already a plugin in RIO:

github.com/multigcs/riocore/tree/dev/riocore/plugins/rmii

but not much tested

but for the tangprimer20k on the dock ext-board there is already a plugin in RIO:

github.com/multigcs/riocore/tree/dev/riocore/plugins/rmii

but not much tested

Please Log in or Create an account to join the conversation.

- meister

- Offline

- Platinum Member

-

Less

More

- Posts: 730

- Thank you received: 445

06 Aug 2024 08:13 #307062

by meister

Replied by meister on topic LinuxCNC-RIO - RealtimeIO for LinuxCNC based on FPGA (ICE40 / ECP5)

i tried to generate a simple udp core and the interface looks very simple:

rgmi_* and sys_* are the FPGA-Pins

udp0_sink and udp0_source the data interface for RX and TX

it looks feasible to connect the whole thing to rio

module liteeth_core (

input wire rgmii_clocks_rx,

output wire rgmii_clocks_tx,

input wire rgmii_int_n,

output wire rgmii_mdc,

input wire rgmii_mdio,

output wire rgmii_rst_n,

input wire rgmii_rx_ctl,

input wire [3:0] rgmii_rx_data,

output wire rgmii_tx_ctl,

output wire [3:0] rgmii_tx_data,

input wire sys_clock,

input wire sys_reset,

input wire [31:0] udp0_sink_data,

input wire udp0_sink_last,

output wire udp0_sink_ready,

input wire udp0_sink_valid,

output wire [31:0] udp0_source_data,

output wire udp0_source_error,

output wire udp0_source_last,

input wire udp0_source_ready,

output wire udp0_source_valid

);udp0_sink and udp0_source the data interface for RX and TX

it looks feasible to connect the whole thing to rio

Please Log in or Create an account to join the conversation.

- Hardware & Machines

- Computers and Hardware

- LinuxCNC-RIO - RealtimeIO for LinuxCNC based on FPGA (ICE40 / ECP5)

Time to create page: 0.188 seconds